Chapter 1: Introduction to the EIU 31

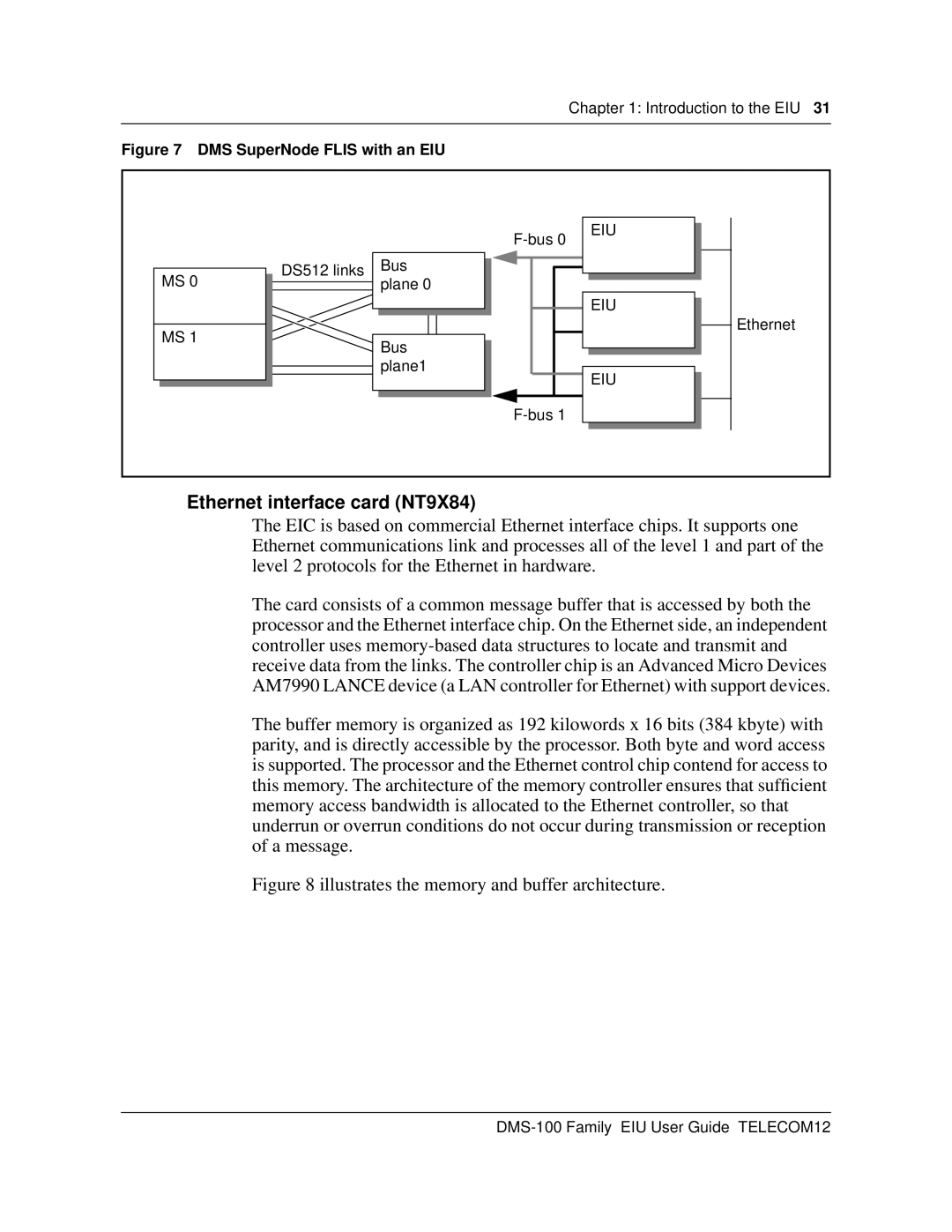

Figure 7 DMS SuperNode FLIS with an EIU

|

| EIU | |

|

|

| |

MS 0 | DS512 links | Bus |

|

plane 0 |

| ||

|

| ||

|

|

| EIU |

MS 1 |

|

| Ethernet |

| Bus |

| |

|

|

| |

|

| plane1 | EIU |

|

|

| |

|

|

|

Ethernet interface card (NT9X84)

The EIC is based on commercial Ethernet interface chips. It supports one Ethernet communications link and processes all of the level 1 and part of the level 2 protocols for the Ethernet in hardware.

The card consists of a common message buffer that is accessed by both the processor and the Ethernet interface chip. On the Ethernet side, an independent controller uses

The buffer memory is organized as 192 kilowords x 16 bits (384 kbyte) with parity, and is directly accessible by the processor. Both byte and word access is supported. The processor and the Ethernet control chip contend for access to this memory. The architecture of the memory controller ensures that sufficient memory access bandwidth is allocated to the Ethernet controller, so that underrun or overrun conditions do not occur during transmission or reception of a message.