C e m b e r 2 0 0

Technical Manual

Trademark Acknowledgment

Organization

Audience

Ansi

Revision Date Remarks

PCI Special Interest Group

Conventions Used in This Manual

Revision Record

ViPreface

Contents

Chapter Signal Descriptions

Chapter Registers

Figures

Contents

Tables

IRDY/, TRDY/, DEVSEL/, STOP/, PERR/, PAR

XivContents

Chapter General Description

Typical LSI53C875A System Application

Benefits of Ultra Scsi

New Features in the LSI53C875A

LSI53C875A Benefits Summary

TolerANT Technology

Scsi Performance

PCI Performance

Integration

Ease of Use

Scripts RAM

Flexibility

Testability

Reliability

Chapter Functional Description

PCI Addressing

PCI Functional Description

Configuration Space

PCI Bus Commands and Functions Supported

CBE30 Command Type Supported as Master Supported as Slave

PCI Bus Commands and Encoding Types for the LSI53C875A

Interrupt Acknowledge Command

Special Cycle Command

Memory Read Command

2.3 I/O Read Command

2.4 I/O Write Command

Reserved Command

Memory Read Multiple Command

Dual Address Cycle DAC Command

Memory Read Line Command

PCI Functional Description

Memory Write and Invalidate Command

PCI Cache Mode

Issuing Cache Commands

Enabling Cache Mode

Memory Write Caching

Memory Read Caching

Host Memory

PCI Cache Mode Alignment

Read Example

Examples

Write Example

Write Example

Memory-to-Memory Moves

Scsi Functional Description

Scripts Processor

Phase Mismatch Handling in Scripts

Internal Scripts RAM

Hardware Control of Scsi Activity LED

3 64-Bit Addressing in Scripts

Designing an Ultra Scsi System

Using the Scsi Clock Quadrupler

Prefetching Scripts Instructions

Load and Store Instructions

Opcode Fetch Burst Capability

Scsi Loopback Mode

Jtag Boundary Scan Testing

Parity Options

Bit Name Location Description

Bits Used for Parity Control and Generation

Scsi Parity Control

Scsi Parity Errors and Interrupts

Parity Checking/Generation

DMA Fifo

Data Paths

DMA Fifo Sections

Asynchronous Scsi Send

LSI53C875A Host Interface Scsi Data Paths

Synchronous Scsi Send

Synchronous Scsi Receive

Asynchronous Scsi Receive

Scsi Termination

Scsi Bus Interface

Regulated Termination for Ultra Scsi

Select/Reselect During Selection/Reselection

Determining the Data Transfer Rate

Synchronous Operation

Determining the Synchronous Transfer Rate

Ultra Scsi Synchronous Data Transfers

Scsi Control Three SCNTL3 Register, Bits 64 SCF20

Scsi Control Three SCNTL3 Register, Bits 20 CCF20

Scsi Transfer Sxfer Register, Bits 75 TP20

Interrupt Handling

Polling and Hardware Interrupts

Registers

Functional Description

Fatal vs. Nonfatal Interrupts

Masking

Stacked Interrupts

Halting in an Orderly Fashion

Read Interrupt Status Zero ISTAT0

Sample Interrupt Service Routine

Chained Block Moves

Wide Scsi Send Bit

Block Move and Chained Block Move Instructions

Wide Scsi Receive Bit

Swide Register

Sodl Register

Chained Block Move Scripts Instruction

Parallel ROM Interface

MAD31 Available Memory Space

Parallel ROM Support

Serial Eeprom Interface

Default Download Mode

Byte Name Description

Power Management

No Download Mode

Mode a Serial Eeprom Data Format

Configuration Register Bits

Power State D0

Power State D1

Power States

Power State D3

Power State D2

Functional Description

Chapter Signal Descriptions

LSI53C875A Functional Signal Grouping

LSI53C875A Functional Signal Grouping

LSI53C875A Internal Pull-ups

Signal Descriptions

Internal Pull-ups on LSI53C875A Signals

Signal Name Pull-up Current Conditions for Pull-up

Type Strength Description

PCI Bus Interface Signals

System Signals

System Signals

Address and Data Signals

Address and Data Signals

Bus Command and Byte Enables are

Interface Control Signals

Interface Control Signals

Initialization Device Select is used as a chip select

Error Reporting Signals

Arbitration Signals

Error Reporting Signals

Arbitration Signals

Interrupt Signal

Scsi Bus Interface Signals

Interrupt Signal

Scsi Bus Interface Signal

10 Scsi Control Signals

Scsi Signals

Scsi Control Signals

Scsi Signals

Scsi General Purpose I/O pin. This pin

Gpio Signals

11 Gpio Signals

Scsi General Purpose I/O pin. Optionally

12 ROM Flash and Memory Interface Signals

ROM Flash and Memory Interface Signals

Test Interface Signals

13 Test Interface Signals

Memory Address/Data Bus. This bus is used

14 Power and Ground Signals

Power and Ground Signals

MAD Bus Programming

15 Decode of MAD Pins

MAD Bus Programming

Signal Descriptions

Chapter Registers

PCI Configuration Registers

Registers

Vendor ID Read Only

VIDVendor ID150

DIDDevice ID150

Command Read/Write

Enable Parity Error Response

Device ID Read Only

EIS

WIE

EBM

EMS

RTA

DPE

SSE

RMA

RIDRevision ID70

Register

DPR

Revision ID Rev ID Read Only

Register 0x0C

Registers 0x09-0x0B

Register 0x0D

Register 0x0E

Register 0x0F

BAR1

BAR0

Registers 0x2C-0x2D

Registers 0x18-0x1B

Registers 0x1C-0x27

Registers 0x28-0x2B

Subsystem ID 150

Registers 0x2E-0x2F

Subsystem ID Read Only

SID

Expansion ROM Base Address Read/Write

Erba

Expansion ROM Base Address 310

Interrupt Line Read/Write ILInterrupt Line70

Registers 0x35-0x3B

Register 0x3C

Capabilities Pointer Read Only CPCapabilities Pointer70

MGMINGNT70

Register 0x3D

Register 0x3E

Register 0x3F

Pmes

APS

D2S

D1S

DSI

Bridge Support Extensions Pmcsrbse Read Only

Dscl

Dslt

PEN

Scsi Registers

Data Read Only

DATAData70

Scsi Register Address Map

Simple Arbitration

ARB10 Arbitration Mode Bits 1

Arbitration Mode

Scsi Control Zero SCNTL0 Read/Write

Start Start Sequence5

Full Arbitration, Selection/Reselection

Watn

EPC

AAP

EXC

ADB

DHP

Iarb

CON

RST

Aesp

SSTStart Scsi Transfer0

Scsi Disconnect Unexpected

Chained Mode

Scsi Control Two SCNTL2 Read/Write

SDU

VUE0

Slpmd

Slphben

WSS

USE

Ultra Scsi Enable

WSRWide Scsi Receive0

Scsi Control Three SCNTL3 Read/Write

CCF20 Clock Conversion Factor

Enable Wide Scsi

SCF20 Synchronous Clock Conversion Factor

EWS

RRE

SRE

ENC

TP20 Scsi Synchronous Transfer Period

Scsi Transfer Sxfer Read/Write

Synch CLK MHz

Transfer Rate

Bits Period ns Mbytes/s

MO40 Max Scsi Synchronous Offset

Synchronous Offset

Maximum Synchronous Offset

Gpio

Scsi Destination ID Sdid Read/Write

Encoded Destination Scsi ID

General Purpose GPREG0 Read/Write

Sfbr Scsi First Byte Received70

Scsi First Byte Received Sfbr Read/Write

SEL

REQ

ACK

BSY

Enid

Register 0x0A

Register 0x0B

VAL

SSEL/ Status

SREQ/ Status

SACK/ Status

SBSY/ Status

SIR

Mdpe

Abrt

SSI

Scsi Registers

ILF

ORF

OLF

AIP

LOA

WOA

Scsi Synchronous Data Fifo Word Count

Bytes or Words

SSTAT2 bit

SDP0L

ILF1

ORF1

OLF1

DSA

SPL1

Ldsc

SDP1

Srst Software Reset6

Interrupt Status Zero ISTAT0 Read/Write

Abort Operation

Semaphore

Signal Process

Sigp

SEM

Dipdma Interrupt Pending0

Sipscsi Interrupt Pending1

Flsh

Srun

Syncirqd

MBOX1 Mailbox One70

Mailbox Zero MBOX0 Read/Write

MBOX0 Mailbox Zero70

Mailbox One MBOX1 Read/Write

FFLByte Full in DMA FIFO70

Chip Test Zero CTEST0 Read/Write

FMTByte Empty in DMA FIFO70

Chip Test One CTEST1 Read Only

Register 0x1A

Ddir

CIO

Teop

Dreq

Dack

Register 0x1B

FLF

CLF

Registers 0x1C-0x1F

Temp

DMA Fifo Dfifo

58Registers

Srtm

Bdis

FBL3

ZSD

Clock Address Incrementor

FBL20 Fifo Byte Control

Chip Test Five CTEST5 Read/Write

Adck

BL2

Bbck

DFS

Masr

DBC

Dfdma FIFO70

Dcmd DMA Command70

DMA Command Dcmd Read/Write

Registers 0x2C-0x2F

Dnad

DSP

Scratcha Scratch Register a 310

DMA Scripts Pointer Save Dsps Read/Write

Dsps DMA Scripts Pointer Save310

Scratch Register a Scratcha Read/Write

BL10 Burst Length

DMA Mode Dmode Read/Write

Siom

Source I/O Memory Enable

Destination I/O Memory Enable

ERLEnable Read Line3

BOF

Enable Read Multiple

Burst Opcode Fetch Enable

Ermp

Illegal Instruction Detected

DMA Interrupt Enable Dien Read/Write

Master Data Parity Error Bus Fault

Scripts Interrupt Instruction Received Reserved

PFF

Register 0x3A

Register 0x3B

Clse

Single Step Mode

SSM

Irqmirq Mode3

COMLSI53C700 Compatibility0

IRQ Disable

STDStart DMA Operation2

Irqd

Registers 0x3C-0x3F

0x40

Adder

UDC

CMP

RSL

SGE

GEN

STO

HTHHandshake-to-Handshake Timer Expired0

Initiator Mode Phase Mismatch Target Mode SATN/ Active

Scsi Interrupt Status Zero SIST0 Read Only

This bit is set when an arbitration only or full arbitration

Scsi Interrupt Status One SIST1 Read Only

Parity Error

Scsi RST/ Received

PAR

Slpar Scsi Longitudinal Parity70

Handshake-to-Handshake Timer Expired

HTH

Scsi Longitudinal Parity Slpar Read/Write

Data Bytes Running Slpar

TYP

Memory Access Control Macntl Read/Write

Scsi Wide Residue Swide Read/Write

Swide Scsi Wide Residue70

Scpts Scripts

DWR

DRD

Pscpt

HTH30 Handshake-to-HandshakeTimer Period

Gpio Enable

Gpiogpio Enable10

Scsi Timer Zero STIME0 Read/Write

SEL30 Selection Time-Out30

Hthba

Gensf

Hthsf

Register 0x4B

Register 0x4A

ART

Register 0x4C

Ssaid

SLT

QEN

Register 0x4D

Sclk

ISO

ROF

Register 0x4E

Qsel

SCE

LOW

SZM

AWS

EXT

STR

Register 0x4F

TTM

Disable Single Initiator Response

Timer Test Mode

S16 Bit System

STW

Scsi Input Data Latch Sidl Read Only

Sidlscsi Input Data Latch150

Lock

Register 0x53

Pmjctl Jump Control6

Enable Phase Mismatch Jump

Chip Control 0 CCNTL0 Read/Write

Enpmj

Enndj

Disfc

Dils

Zmode

Ddac

64TIMOD

Scsi Bus Data Lines Sbdl Read Only

Enable 64-Bit Direct Bmov

EN64TIBMV

EN64DBMV

Registers 0x60-0x9F

64-Bit Scripts Selectors

Register 0x5A-0x5B

Registers 0x5C-0x5F

Memory Move Read Selector Mmrs

Registers 0xA0-0xA3

Memory Move Read Selector Mmrs Read/Write

Mmrs

SFS

Registers 0xA4-0xA7

Registers 0xA8-0xAB

Mmws

Sbms

Registers 0xAC-0xAF

Registers 0xB0-0xB3

DRS

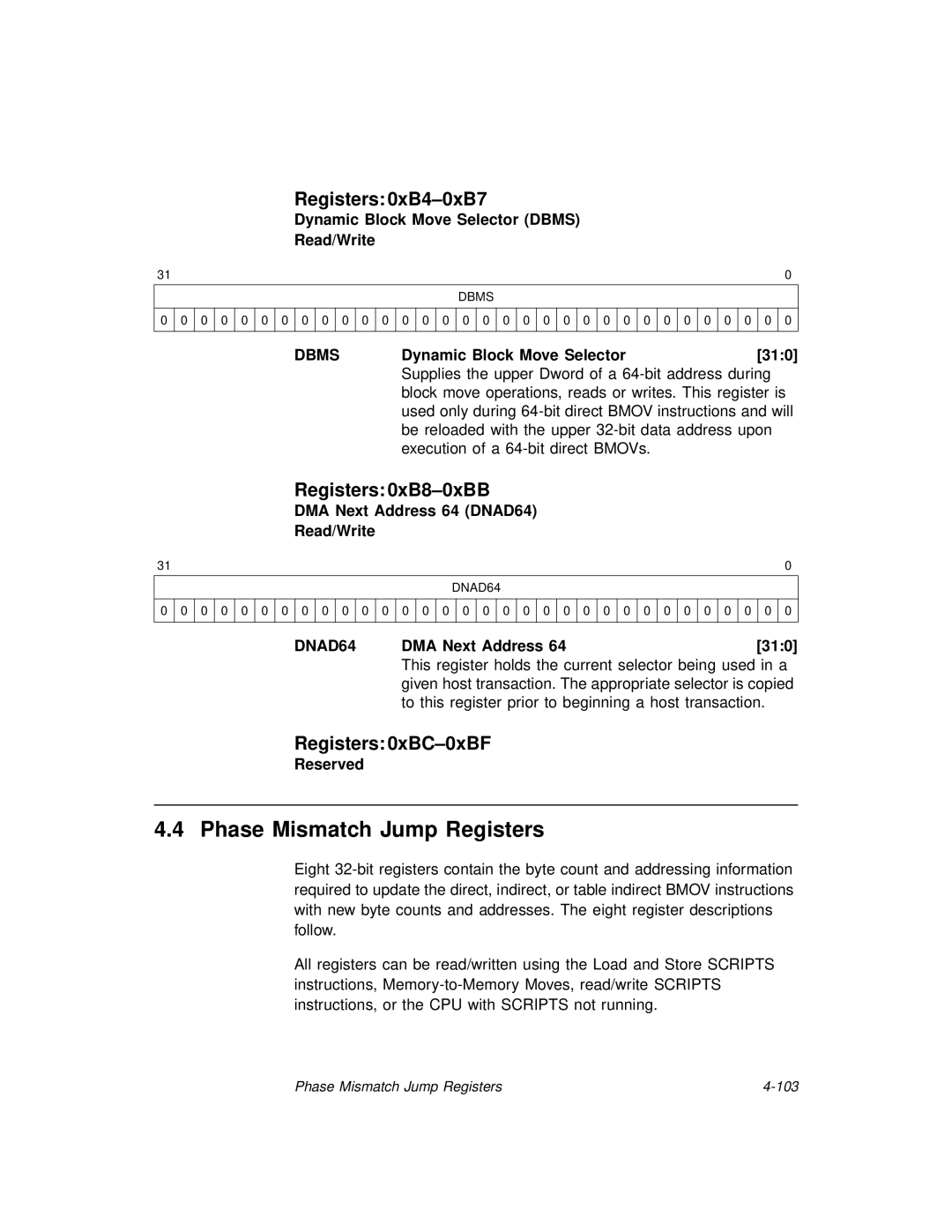

Registers 0xBC-0xBF

Phase Mismatch Jump Registers

Registers 0xB4-0xB7

Registers 0xB8-0xBB

PMJAD2

Registers 0xC0-0xC3

Registers 0xC4-0xC7

PMJAD1

Registers 0xC8-0xCB

Registers 0xCC-0xCF

RBC

Entry Storage Address 310

Registers 0xD0-0xD3

Entry Storage Address ESA Read/Write

ESA

Registers 0xD4-0xD7

Registers 0xD8-0xDA

SBC

Csbc

Register 0xDB

Registers 0xDC-0xDF

Registers 0xE0-0xFF

Scsi Scripts

Low Level Register Interface Mode

High Level Scsi Scripts Mode

Sample Operation

Scripts Instructions

Instruction Description

Scsi Scripts Instruction Set

Scripts Overview

First Dword

Block Move Instruction

Direct Addressing

TIA

Table Indirect Bit Addressing

Command Not Used Don’t Care

Target Mode

OPCOpCode27

OPC Instruction Defined

Initiator Mode

SCSIP20 Scsi Phase2624

Scsi Information Transfer Phase

Scsi Phase

TC230 Transfer Counter230

Start Address 310

Target Mode Initiator Mode

I/O Instruction

Second Dword

Instruction Defined

IT10 Instruction Type I/O Instruction 3130

OPC20 OpCode 2927

Reselect Instruction

Clear Instruction

Disconnect Instruction

Wait Select Instruction

Set Instruction

Select Instruction

Wait Reselect Instruction

Wait Disconnect Instruction

TITable Indirect Mode25

Relative Addressing Mode

Bit

Direct

Table Indirect

Relative

Table Relative

Command Table Offset Absolute Jump Offset

Set/Clear Satn

Set/Clear Sack Reserved

Use data8/SFBR

Read/Write Instructions

IT10 Instruction Type Read/Write Instruction 3130

O20 Operator 2624

A60 Register Address A60 2216

Read-Modify-Write Cycles

Read/Write Instructions

Move To/From Sfbr Cycles

Transfer Control Instructions

IT10 Instruction Type Transfer Control 3130

Transfer Control Instructions

Jump Instruction

Return Instruction

Call Instruction

Interrupt-on-the-Fly Instruction

Interrupt Instruction

Jump/Call a Relative Address

Scsi Phase Comparisons

RARelative Addressing Mode23

Jump/Call an Absolute Address

Bit 2 is asserted

JMP

Jump If True/False

WVP

Compare Phase

Wait for Valid Phase

Compare Data

Jump Address 310

Memory Move Instructions

DCV

Data Compare Value

IT20 Instruction Type Memory Move 3129

Reserved 2825

No Flush

Dsps Register 310

Read/Write System Memory from Scripts

Bit A1 Bit A0 Number of Bytes Allowed to Load and Store

Load and Store Instructions

Third Dword

Temp Register 310

Bit Source Destination

IT20 Instruction Type 3129

DSA Relative

Reserved 2726 No Flush Store instruction only

DMA Control Dcntl register is set

This bit has no effect unless the Prefetch Enable bit

Scsi Scripts Instruction Set

DC Characteristics

Chapter Electrical Specifications

Input Capacitance

Symbol Parameter Min Max Unit Test Conditions

Absolute Maximum Stress Ratings1

Operating Conditions1

Bidirectional Signals-GPIO0FETCH/, GPIO1MASTER/, GPIO24

Bidirectional Signals-MAD70, MAS/10, MCE/, MOE/, MWE

Output Signal-TDO

TolerANT Technology Electrical Characteristics

Output Signals-IRQ/, MAC/TESTOUT, REQ

Output Signal-SERR

Pqfp

Symbol Parameter Min1 Max Unit Test Conditions

Rise and Fall Time Test Condition

Input Current as a Function of Input Voltage

AC Characteristics

Symbol Parameter Min Max Unit

12 External Clock1

Interrupt Output

Reset Input

PCI and External Memory Interface Timing Diagrams

Electrical Specifications

15 PCI Configuration Register Read

PCI Configuration Register Read

Target Timing

10 PCI Configuration Register Write

16 PCI Configuration Register Write

11 32-Bit Operating Register/SCRIPTS RAM Read

17 32-Bit Operating Register/SCRIPTS RAM Read

12 64-Bit Address Operating Register/SCRIPTS RAM Read

18 64-Bit Address Operating Register/SCRIPTS RAM Read

13 32-Bit Operating Register/SCRIPTS RAM Write

19 32-Bit Operating Register/SCRIPTS RAM Write

14 64-Bit Address Operating Register/SCRIPTS RAM Write

20 64-Bit Address Operating Register/SCRIPTS RAM Write

21 Nonburst Opcode Fetch, 32-Bit Address and Data

Initiator Timing

15 Nonburst Opcode Fetch, 32-Bit Address and Data

22 Burst Opcode Fetch, 32-Bit Address and Data

16 Burst Opcode Fetch, 32-Bit Address and Data

23 Back-to-Back Read, 32-Bit Address and Data

17 Back-to-Back Read, 32-Bit Address and Data

24 Back-to-Back Write, 32-Bit Address and Data

18 Back-to-Back Write, 32-Bit Address and Data

25 Burst Read, 32-Bit Address and Data

19 Burst Read, 32-Bit Address and Data

26 Burst Read, 64-Bit Address and Data

20 Burst Read, 64-Bit Address and Data

27 Burst Write, 32-Bit Address and Data

21 Burst Write, 32-Bit Address and Data

28 Burst Write, 64-Bit Address and 32-Bit Data

22 Burst Write, 64-Bit Address and 32-Bit Data

29 External Memory Read

External Memory Timing

23 External Memory Read

STOP/ Driven by LSI53C875A

30 External Memory Write

External Memory Write timings start on

24 External Memory Write

Data Byte Enable

Address out from MOE/, MCE/ High

Driven by LSI53C875A Higher Valid Write Data

CBE30 Byte Enable

Data Byte Enable Out Lower Address

Data LSI53C875A-Data

Data Byte Enable Data Out

Slow Memory ≤ 128 Kbytes Read Cycle

Symbol Parameter Min

30 Slow Memory ≤ 128 Kbytes Write Cycle

Slow Memory ≤ 128 Kbytes Write Cycle

≤ 64 Kbytes ROM Read Cycle

32 ≤ 64 Kbyte ROM Write Cycle

≤ 64 Kbyte ROM Write Cycle

37 Initiator Asynchronous Send

Scsi Timing Diagrams

34 Initiator Asynchronous Receive

38 Initiator Asynchronous Receive

35 Target Asynchronous Send

39 Target Asynchronous Send

41 SCSI-1 Transfers 5.0 Mbytes

40 Target Asynchronous Receive

Symbol Parameter Min Max Unit

37 Initiator and Target Synchronous Transfer

38 LSI53C875A 160-Pin Pqfp Mechanical Drawing

Package Diagrams

Pin Pqfp P3 Mechanical Drawing Sheet 2

44 160 Pqfp Pin List by Location

Signal Pin

Pin BGA Mechanical Drawing

NC1

45 169 BGA Pin List by Location

Appendix a Register Summary

Table A.2 LSI53C875A Scsi Register Map

Register Summary

Scratch Registers C-RSCRATCHC-SCRATCHR

Table A.2 LSI53C875A Scsi Register Map

Register Summary

Appendix B External Memory Interface Diagram Examples

Figure B.2 64 Kbyte Interface with 150 ns Memory

External Memory Interface Diagram Examples

Figure B.4 512 Kbyte Interface with 150 ns Memory

Index

Symbols

IX-2Index

SGE 4-74,4-77 SI

Numerics

IX-4Index

IX-5

IX-6Index

IX-7

IX-8Index

IX-9

IX-10Index

Customer Feedback

Excellent Good Average Fair Poor

Reader’s Comments

California

Distributors by State

New York

Direct Sales Representatives by State Component and HAB

North America

Sales Offices and Design Resource Centers

Korea

Australia Hong Kong

International Distributors