www.ti.com | EMAC Port Registers |

5.11 MAC Input Vector Register (MACINVECTOR)

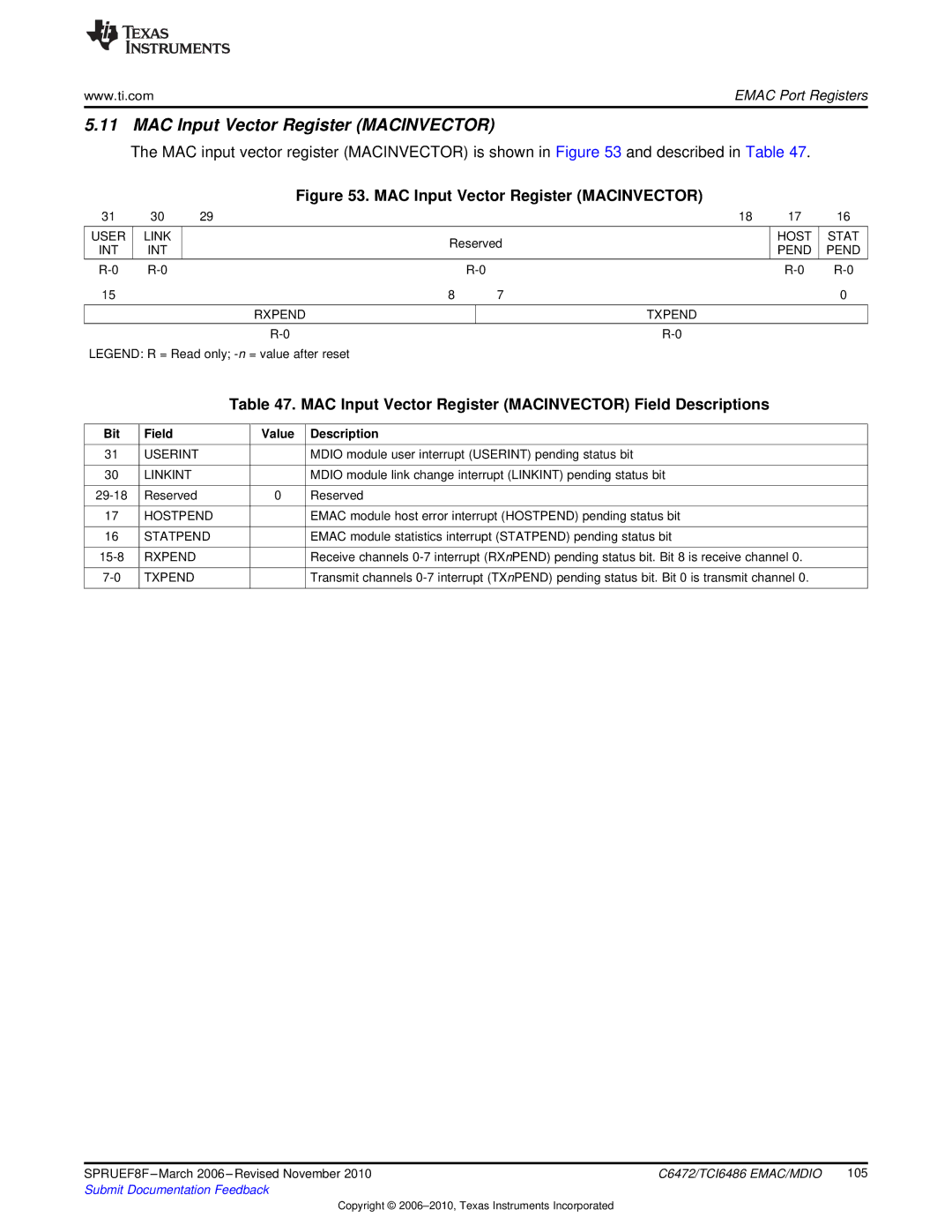

The MAC input vector register (MACINVECTOR) is shown in Figure 53 and described in Table 47.

Figure 53. MAC Input Vector Register (MACINVECTOR)

31 | 30 | 29 |

|

| 18 | 17 | 16 |

USER | LINK | Reserved |

| HOST | STAT | ||

INT | INT |

| PEND | PEND | |||

|

|

|

| ||||

|

|

|

|

|

|

| |

|

| ||||||

15 |

| 8 | 7 |

|

| 0 | |

|

|

|

|

|

|

|

|

|

| RXPEND |

|

| TXPEND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

LEGEND: R = Read only;

Table 47. MAC Input Vector Register (MACINVECTOR) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

31 | USERINT |

| MDIO module user interrupt (USERINT) pending status bit |

|

|

|

|

30 | LINKINT |

| MDIO module link change interrupt (LINKINT) pending status bit |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

17 | HOSTPEND |

| EMAC module host error interrupt (HOSTPEND) pending status bit |

|

|

|

|

16 | STATPEND |

| EMAC module statistics interrupt (STATPEND) pending status bit |

|

|

|

|

RXPEND |

| Receive channels | |

|

|

|

|

TXPEND |

| Transmit channels | |

|

|

|

|

SPRUEF8F | C6472/TCI6486 EMAC/MDIO | 105 |

Submit Documentation Feedback |

|

|

Copyright ©