EMAC Port Registers | www.ti.com |

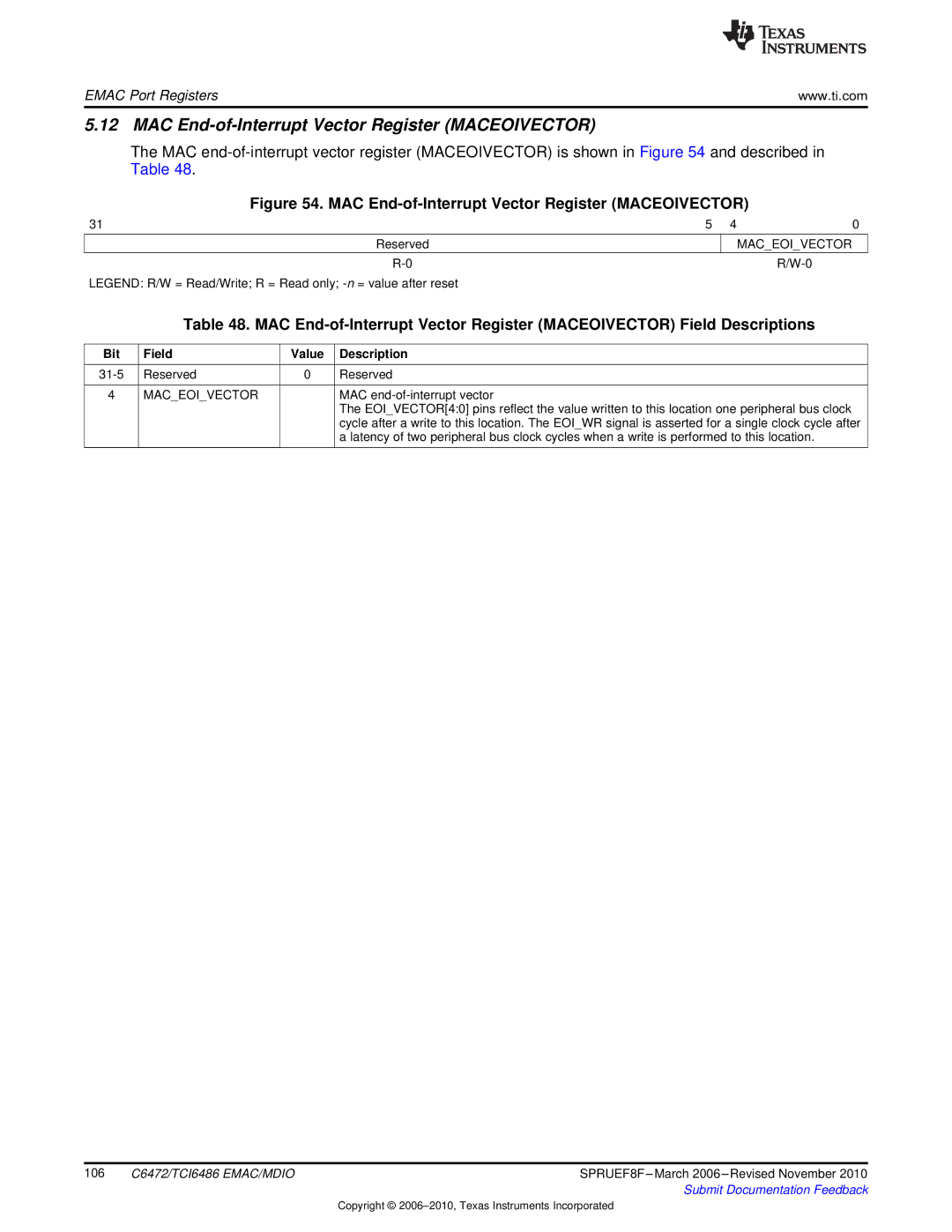

5.12 MAC End-of-Interrupt Vector Register (MACEOIVECTOR)

The MAC

Figure 54. MAC End-of-Interrupt Vector Register (MACEOIVECTOR)

31 | 5 | 4 | 0 |

Reserved |

|

| MAC_EOI_VECTOR |

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

Table 48. MAC

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

4 | MAC_EOI_VECTOR |

| MAC |

|

|

| The EOI_VECTOR[4:0] pins reflect the value written to this location one peripheral bus clock |

|

|

| cycle after a write to this location. The EOI_WR signal is asserted for a single clock cycle after |

|

|

| a latency of two peripheral bus clock cycles when a write is performed to this location. |

|

|

|

|

106 | C6472/TCI6486 EMAC/MDIO | SPRUEF8F |

|

| Submit Documentation Feedback |

Copyright ©