www.ti.comEMAC Port Registers

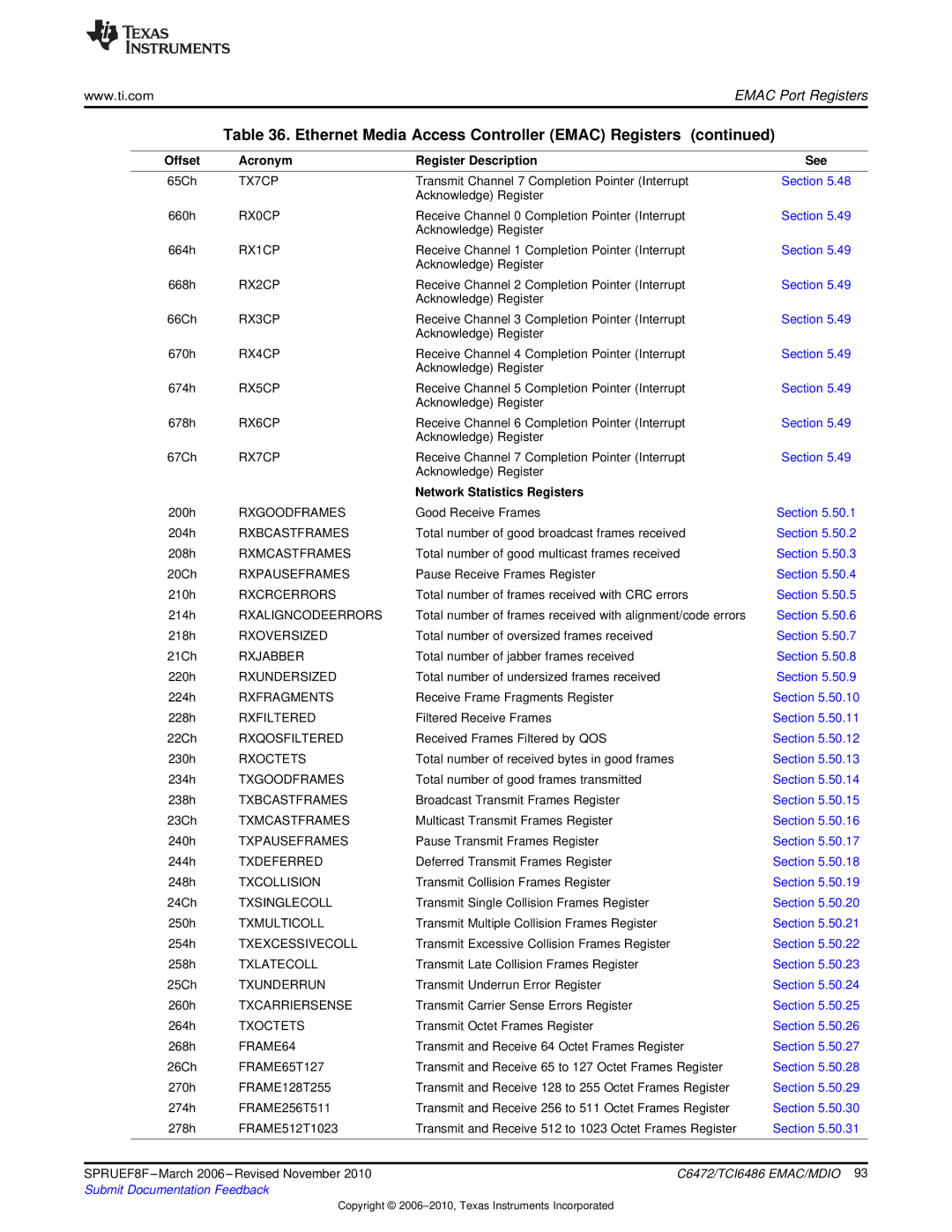

Table 36. Ethernet Media Access Controller (EMAC) Registers (continued)

| Offset | Acronym | Register Description | See |

| 65Ch | TX7CP | Transmit Channel 7 Completion Pointer (Interrupt | Section 5.48 |

|

|

| Acknowledge) Register |

|

| 660h | RX0CP | Receive Channel 0 Completion Pointer (Interrupt | Section 5.49 |

|

|

| Acknowledge) Register |

|

| 664h | RX1CP | Receive Channel 1 Completion Pointer (Interrupt | Section 5.49 |

|

|

| Acknowledge) Register |

|

| 668h | RX2CP | Receive Channel 2 Completion Pointer (Interrupt | Section 5.49 |

|

|

| Acknowledge) Register |

|

| 66Ch | RX3CP | Receive Channel 3 Completion Pointer (Interrupt | Section 5.49 |

|

|

| Acknowledge) Register |

|

| 670h | RX4CP | Receive Channel 4 Completion Pointer (Interrupt | Section 5.49 |

|

|

| Acknowledge) Register |

|

| 674h | RX5CP | Receive Channel 5 Completion Pointer (Interrupt | Section 5.49 |

|

|

| Acknowledge) Register |

|

| 678h | RX6CP | Receive Channel 6 Completion Pointer (Interrupt | Section 5.49 |

|

|

| Acknowledge) Register |

|

| 67Ch | RX7CP | Receive Channel 7 Completion Pointer (Interrupt | Section 5.49 |

|

|

| Acknowledge) Register |

|

|

|

| Network Statistics Registers |

|

| 200h | RXGOODFRAMES | Good Receive Frames | Section 5.50.1 |

| 204h | RXBCASTFRAMES | Total number of good broadcast frames received | Section 5.50.2 |

| 208h | RXMCASTFRAMES | Total number of good multicast frames received | Section 5.50.3 |

| 20Ch | RXPAUSEFRAMES | Pause Receive Frames Register | Section 5.50.4 |

| 210h | RXCRCERRORS | Total number of frames received with CRC errors | Section 5.50.5 |

| 214h | RXALIGNCODEERRORS | Total number of frames received with alignment/code errors | Section 5.50.6 |

| 218h | RXOVERSIZED | Total number of oversized frames received | Section 5.50.7 |

| 21Ch | RXJABBER | Total number of jabber frames received | Section 5.50.8 |

| 220h | RXUNDERSIZED | Total number of undersized frames received | Section 5.50.9 |

| 224h | RXFRAGMENTS | Receive Frame Fragments Register | Section 5.50.10 |

| 228h | RXFILTERED | Filtered Receive Frames | Section 5.50.11 |

| 22Ch | RXQOSFILTERED | Received Frames Filtered by QOS | Section 5.50.12 |

| 230h | RXOCTETS | Total number of received bytes in good frames | Section 5.50.13 |

| 234h | TXGOODFRAMES | Total number of good frames transmitted | Section 5.50.14 |

| 238h | TXBCASTFRAMES | Broadcast Transmit Frames Register | Section 5.50.15 |

| 23Ch | TXMCASTFRAMES | Multicast Transmit Frames Register | Section 5.50.16 |

| 240h | TXPAUSEFRAMES | Pause Transmit Frames Register | Section 5.50.17 |

| 244h | TXDEFERRED | Deferred Transmit Frames Register | Section 5.50.18 |

| 248h | TXCOLLISION | Transmit Collision Frames Register | Section 5.50.19 |

| 24Ch | TXSINGLECOLL | Transmit Single Collision Frames Register | Section 5.50.20 |

| 250h | TXMULTICOLL | Transmit Multiple Collision Frames Register | Section 5.50.21 |

| 254h | TXEXCESSIVECOLL | Transmit Excessive Collision Frames Register | Section 5.50.22 |

| 258h | TXLATECOLL | Transmit Late Collision Frames Register | Section 5.50.23 |

| 25Ch | TXUNDERRUN | Transmit Underrun Error Register | Section 5.50.24 |

| 260h | TXCARRIERSENSE | Transmit Carrier Sense Errors Register | Section 5.50.25 |

| 264h | TXOCTETS | Transmit Octet Frames Register | Section 5.50.26 |

| 268h | FRAME64 | Transmit and Receive 64 Octet Frames Register | Section 5.50.27 |

| 26Ch | FRAME65T127 | Transmit and Receive 65 to 127 Octet Frames Register | Section 5.50.28 |

| 270h | FRAME128T255 | Transmit and Receive 128 to 255 Octet Frames Register | Section 5.50.29 |

| 274h | FRAME256T511 | Transmit and Receive 256 to 511 Octet Frames Register | Section 5.50.30 |

| 278h | FRAME512T1023 | Transmit and Receive 512 to 1023 Octet Frames Register | Section 5.50.31 |

|

|

| ||

|

|

|

|

|

SPRUEF8F | C6472/TCI6486 EMAC/MDIO 93 | |||

Submit Documentation Feedback |

|

| ||

Copyright ©