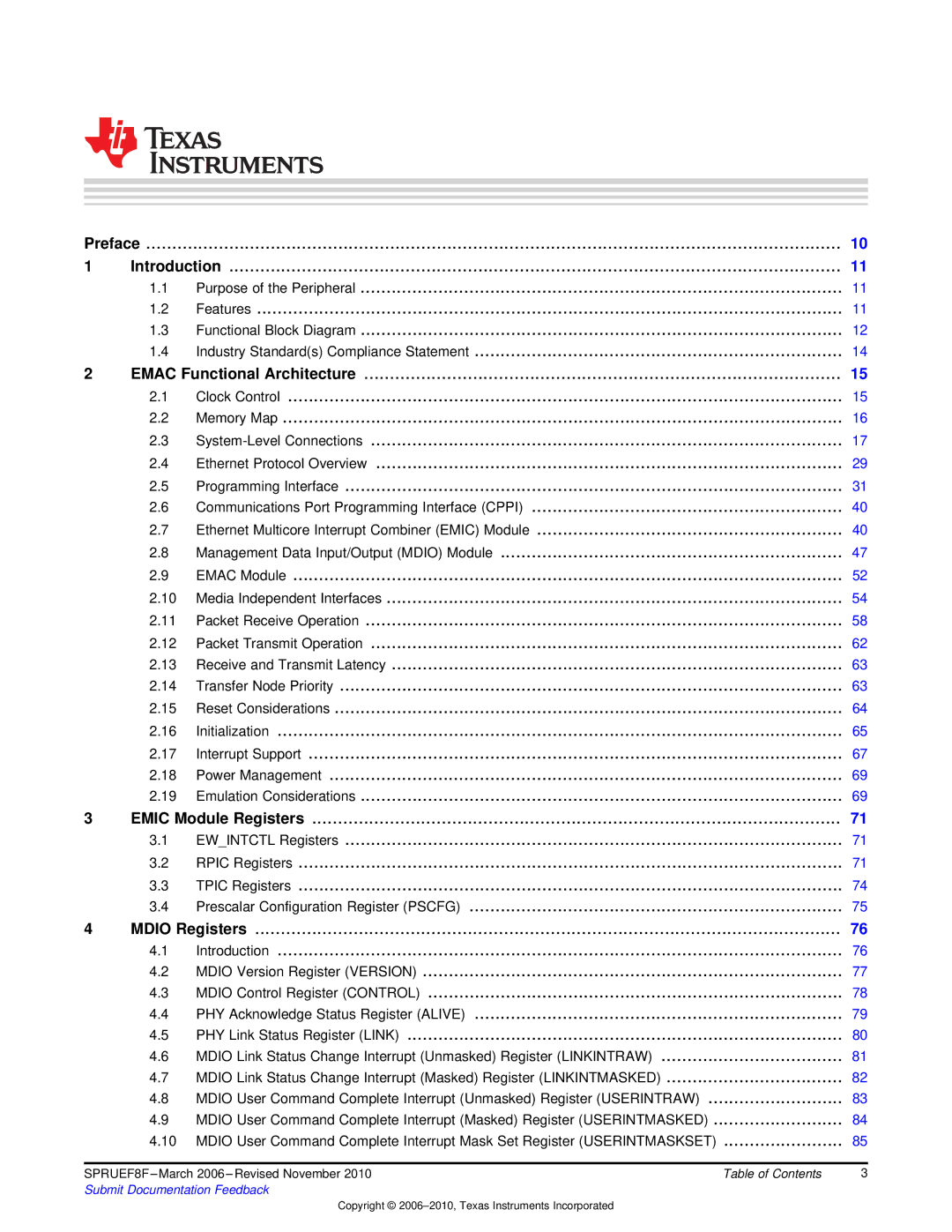

Preface |

| 10 | ||

1 | Introduction | 11 | ||

| 1.1 | Purpose of the Peripheral | 11 | |

| 1.2 | Features | 11 | |

| 1.3 | Functional Block Diagram | 12 | |

| 1.4 | Industry Standard(s) Compliance Statement | 14 | |

2 | EMAC Functional Architecture | 15 | ||

| 2.1 | Clock Control | 15 | |

| 2.2 | Memory Map | 16 | |

| 2.3 | 17 | ||

| 2.4 | Ethernet Protocol Overview | 29 | |

| 2.5 | Programming Interface | 31 | |

| 2.6 | Communications Port Programming Interface (CPPI) | 40 | |

| 2.7 | Ethernet Multicore Interrupt Combiner (EMIC) Module | 40 | |

| 2.8 | Management Data Input/Output (MDIO) Module | 47 | |

| 2.9 | EMAC Module | 52 | |

| 2.10 | Media Independent Interfaces | 54 | |

| 2.11 | Packet Receive Operation | 58 | |

| 2.12 | Packet Transmit Operation | 62 | |

| 2.13 | Receive and Transmit Latency | 63 | |

| 2.14 | Transfer Node Priority | 63 | |

| 2.15 | Reset Considerations | 64 | |

| 2.16 | Initialization | 65 | |

| 2.17 | Interrupt Support | 67 | |

| 2.18 | Power Management | 69 | |

| 2.19 | Emulation Considerations | 69 | |

3 | EMIC Module Registers | 71 | ||

| 3.1 | EW_INTCTL Registers | 71 | |

| 3.2 | RPIC Registers | 71 | |

| 3.3 | TPIC Registers | 74 | |

| 3.4 | Prescalar Configuration Register (PSCFG) | 75 | |

4 | MDIO Registers | 76 | ||

| 4.1 | Introduction | 76 | |

| 4.2 | MDIO Version Register (VERSION) | 77 | |

| 4.3 | MDIO Control Register (CONTROL) | 78 | |

| 4.4 | PHY Acknowledge Status Register (ALIVE) | 79 | |

| 4.5 | PHY Link Status Register (LINK) | 80 | |

| 4.6 | MDIO Link Status Change Interrupt (Unmasked) Register (LINKINTRAW) | 81 | |

| 4.7 | MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED) | 82 | |

| 4.8 | MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW) | 83 | |

| 4.9 | MDIO User Command Complete Interrupt (Masked) Register (USERINTMASKED) | 84 | |

| 4.10 | MDIO User Command Complete Interrupt Mask Set Register (USERINTMASKSET) | ....................... | 85 |

|

|

| ||

SPRUEF8F | Table of Contents | 3 | ||

Submit Documentation Feedback |

|

| ||

Copyright ©