www.ti.com |

|

|

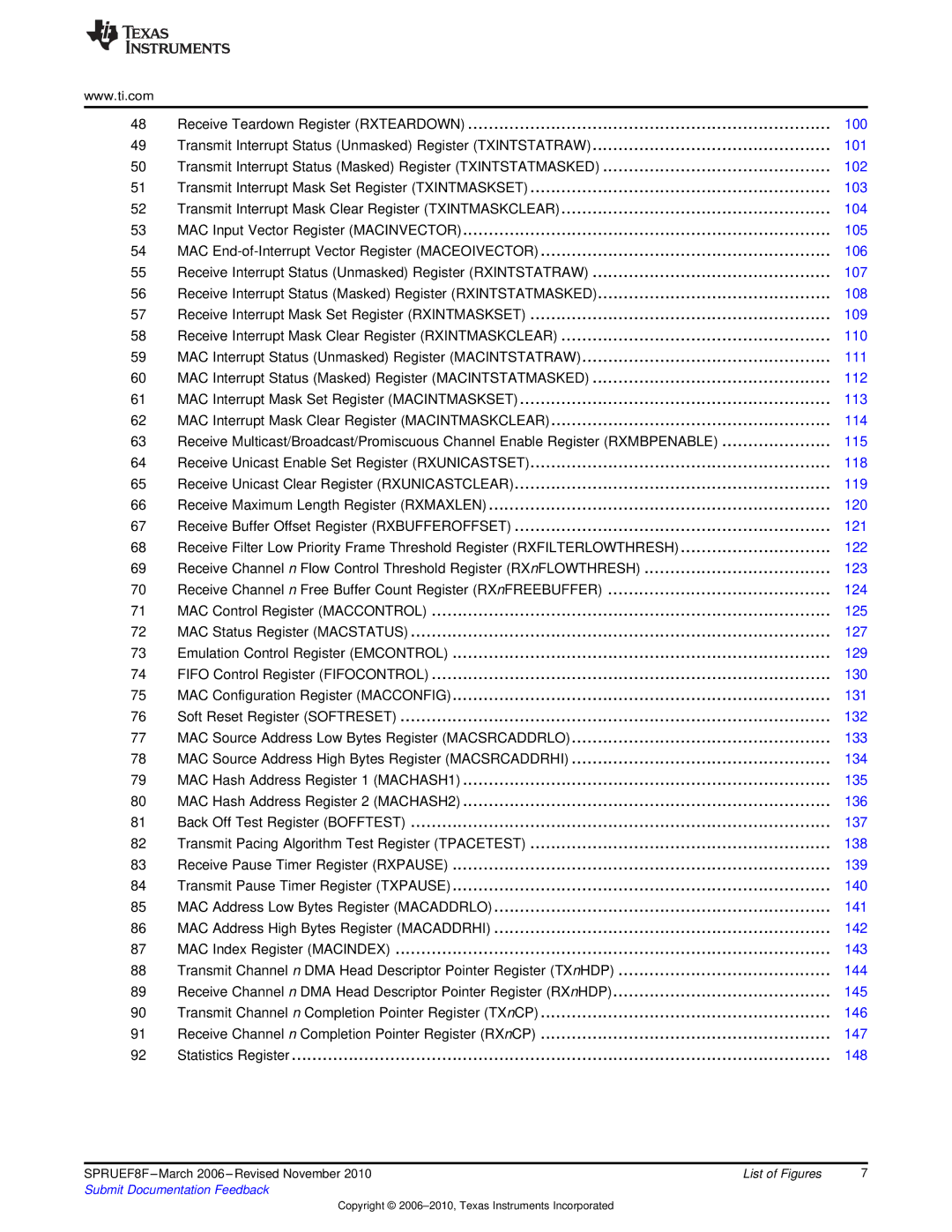

48 | Receive Teardown Register (RXTEARDOWN) | 100 |

49 | Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW) | 101 |

50 | Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) | 102 |

51 | Transmit Interrupt Mask Set Register (TXINTMASKSET) | 103 |

52 | Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR) | 104 |

53 | MAC Input Vector Register (MACINVECTOR) | 105 |

54 | MAC | 106 |

55 | Receive Interrupt Status (Unmasked) Register (RXINTSTATRAW) | 107 |

56 | Receive Interrupt Status (Masked) Register (RXINTSTATMASKED) | 108 |

57 | Receive Interrupt Mask Set Register (RXINTMASKSET) | 109 |

58 | Receive Interrupt Mask Clear Register (RXINTMASKCLEAR) | 110 |

59 | MAC Interrupt Status (Unmasked) Register (MACINTSTATRAW) | 111 |

60 | MAC Interrupt Status (Masked) Register (MACINTSTATMASKED) | 112 |

61 | MAC Interrupt Mask Set Register (MACINTMASKSET) | 113 |

62 | MAC Interrupt Mask Clear Register (MACINTMASKCLEAR) | 114 |

63 | Receive Multicast/Broadcast/Promiscuous Channel Enable Register (RXMBPENABLE) | 115 |

64 | Receive Unicast Enable Set Register (RXUNICASTSET) | 118 |

65 | Receive Unicast Clear Register (RXUNICASTCLEAR) | 119 |

66 | Receive Maximum Length Register (RXMAXLEN) | 120 |

67 | Receive Buffer Offset Register (RXBUFFEROFFSET) | 121 |

68 | Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH) | 122 |

69 | Receive Channel n Flow Control Threshold Register (RXnFLOWTHRESH) | 123 |

70 | Receive Channel n Free Buffer Count Register (RXnFREEBUFFER) | 124 |

71 | MAC Control Register (MACCONTROL) | 125 |

72 | MAC Status Register (MACSTATUS) | 127 |

73 | Emulation Control Register (EMCONTROL) | 129 |

74 | FIFO Control Register (FIFOCONTROL) | 130 |

75 | MAC Configuration Register (MACCONFIG) | 131 |

76 | Soft Reset Register (SOFTRESET) | 132 |

77 | MAC Source Address Low Bytes Register (MACSRCADDRLO) | 133 |

78 | MAC Source Address High Bytes Register (MACSRCADDRHI) | 134 |

79 | MAC Hash Address Register 1 (MACHASH1) | 135 |

80 | MAC Hash Address Register 2 (MACHASH2) | 136 |

81 | Back Off Test Register (BOFFTEST) | 137 |

82 | Transmit Pacing Algorithm Test Register (TPACETEST) | 138 |

83 | Receive Pause Timer Register (RXPAUSE) | 139 |

84 | Transmit Pause Timer Register (TXPAUSE) | 140 |

85 | MAC Address Low Bytes Register (MACADDRLO) | 141 |

86 | MAC Address High Bytes Register (MACADDRHI) | 142 |

87 | MAC Index Register (MACINDEX) | 143 |

88 | Transmit Channel n DMA Head Descriptor Pointer Register (TXnHDP) | 144 |

89 | Receive Channel n DMA Head Descriptor Pointer Register (RXnHDP) | 145 |

90 | Transmit Channel n Completion Pointer Register (TXnCP) | 146 |

91 | Receive Channel n Completion Pointer Register (RXnCP) | 147 |

92 | Statistics Register | 148 |

SPRUEF8F | List of Figures | 7 |

Submit Documentation Feedback |

|

|

Copyright ©