EMIC Module Registers | www.ti.com |

3.3TPIC Registers

3.3.1TPCFG Registers

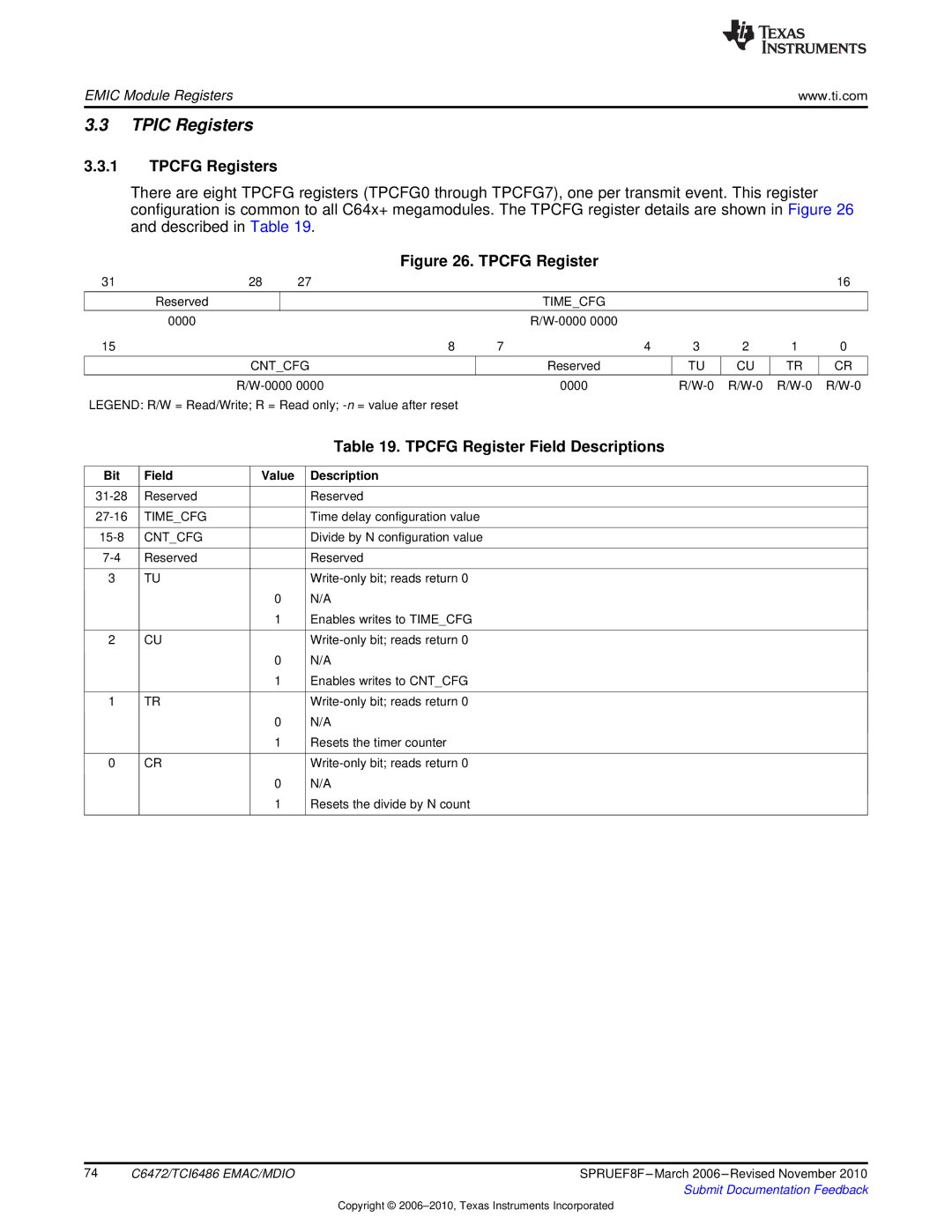

There are eight TPCFG registers (TPCFG0 through TPCFG7), one per transmit event. This register configuration is common to all C64x+ megamodules. The TPCFG register details are shown in Figure 26 and described in Table 19.

Figure 26. TPCFG Register

31 | 28 | 27 |

|

|

|

|

| 16 |

| Reserved |

|

| TIME_CFG |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0000 |

|

|

|

|

|

| |

15 |

| 8 | 7 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

| CNT_CFG |

| Reserved | TU | CU | TR | CR | |

|

|

|

|

|

|

|

|

|

|

| 0000 | ||||||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

|

|

| ||

|

|

| Table 19. TPCFG Register Field Descriptions |

|

|

|

|

Bit | Field | Value | Description |

|

|

|

|

Reserved |

| Reserved | |

|

|

|

|

TIME_CFG |

| Time delay configuration value | |

|

|

|

|

CNT_CFG |

| Divide by N configuration value | |

|

|

|

|

Reserved |

| Reserved | |

|

|

|

|

3 | TU |

| |

|

| 0 | N/A |

|

| 1 | Enables writes to TIME_CFG |

|

|

|

|

2 | CU |

| |

|

| 0 | N/A |

|

| 1 | Enables writes to CNT_CFG |

|

|

|

|

1 | TR |

| |

|

| 0 | N/A |

|

| 1 | Resets the timer counter |

|

|

|

|

0 | CR |

| |

|

| 0 | N/A |

|

| 1 | Resets the divide by N count |

|

|

|

|

74 | C6472/TCI6486 EMAC/MDIO | SPRUEF8F |

|

| Submit Documentation Feedback |

Copyright ©