MDIO Registers | www.ti.com |

4.13 MDIO User PHY Select Register 0 (USERPHYSEL0)

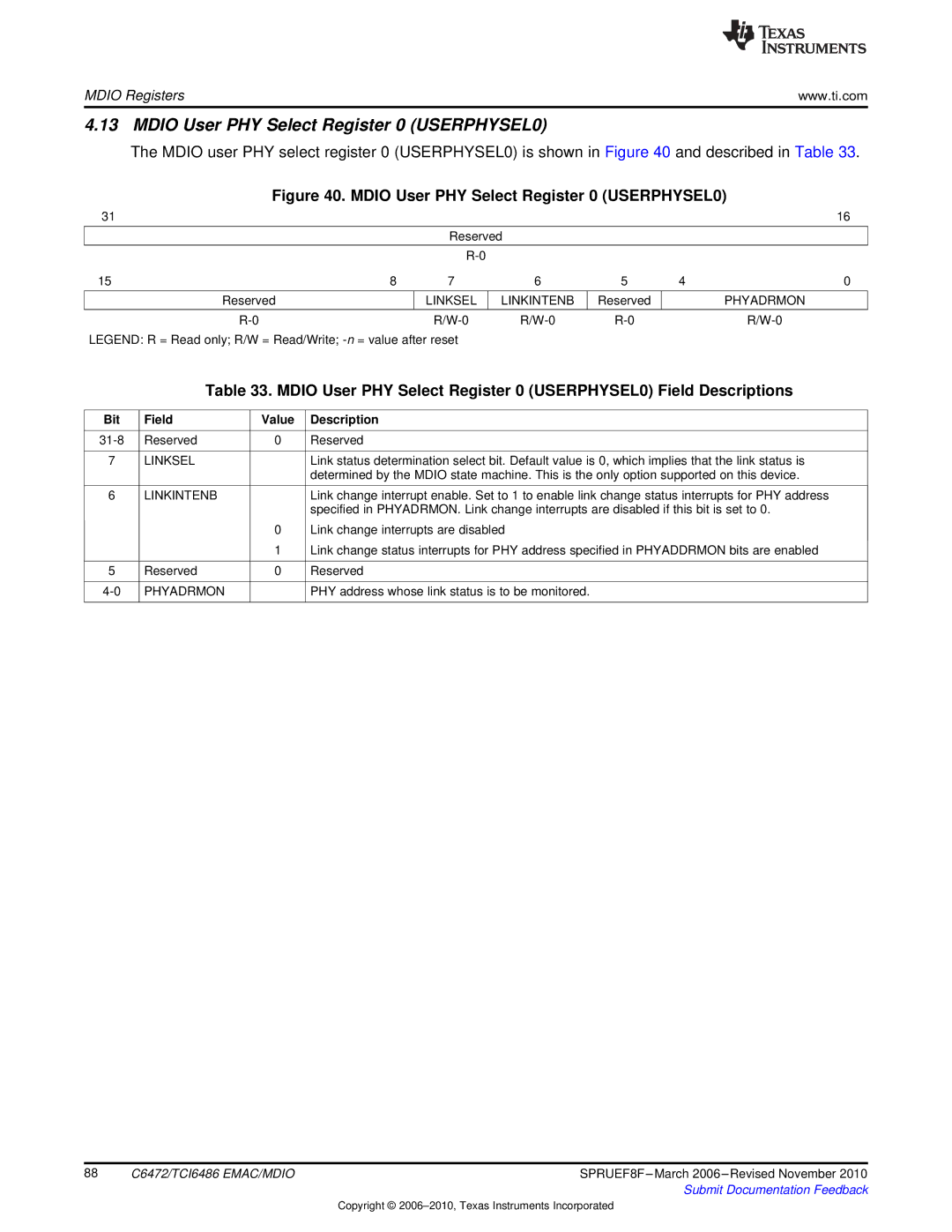

The MDIO user PHY select register 0 (USERPHYSEL0) is shown in Figure 40 and described in Table 33.

Figure 40. MDIO User PHY Select Register 0 (USERPHYSEL0)

31 |

|

|

|

|

| 16 |

|

| Reserved |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

15 | 8 | 7 | 6 | 5 | 4 | 0 |

|

|

|

|

|

|

|

Reserved |

| LINKSEL | LINKINTENB | Reserved |

| PHYADRMON |

|

|

|

|

|

|

|

|

| |||||

LEGEND: R = Read only; R/W = Read/Write;

Table 33. MDIO User PHY Select Register 0 (USERPHYSEL0) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

7 | LINKSEL |

| Link status determination select bit. Default value is 0, which implies that the link status is |

|

|

| determined by the MDIO state machine. This is the only option supported on this device. |

|

|

|

|

6 | LINKINTENB |

| Link change interrupt enable. Set to 1 to enable link change status interrupts for PHY address |

|

|

| specified in PHYADRMON. Link change interrupts are disabled if this bit is set to 0. |

|

| 0 | Link change interrupts are disabled |

|

| 1 | Link change status interrupts for PHY address specified in PHYADDRMON bits are enabled |

|

|

|

|

5 | Reserved | 0 | Reserved |

|

|

|

|

PHYADRMON |

| PHY address whose link status is to be monitored. | |

|

|

|

|

88 | C6472/TCI6486 EMAC/MDIO | SPRUEF8F |

|

| Submit Documentation Feedback |

Copyright ©