EMAC Functional Architecture | www.ti.com |

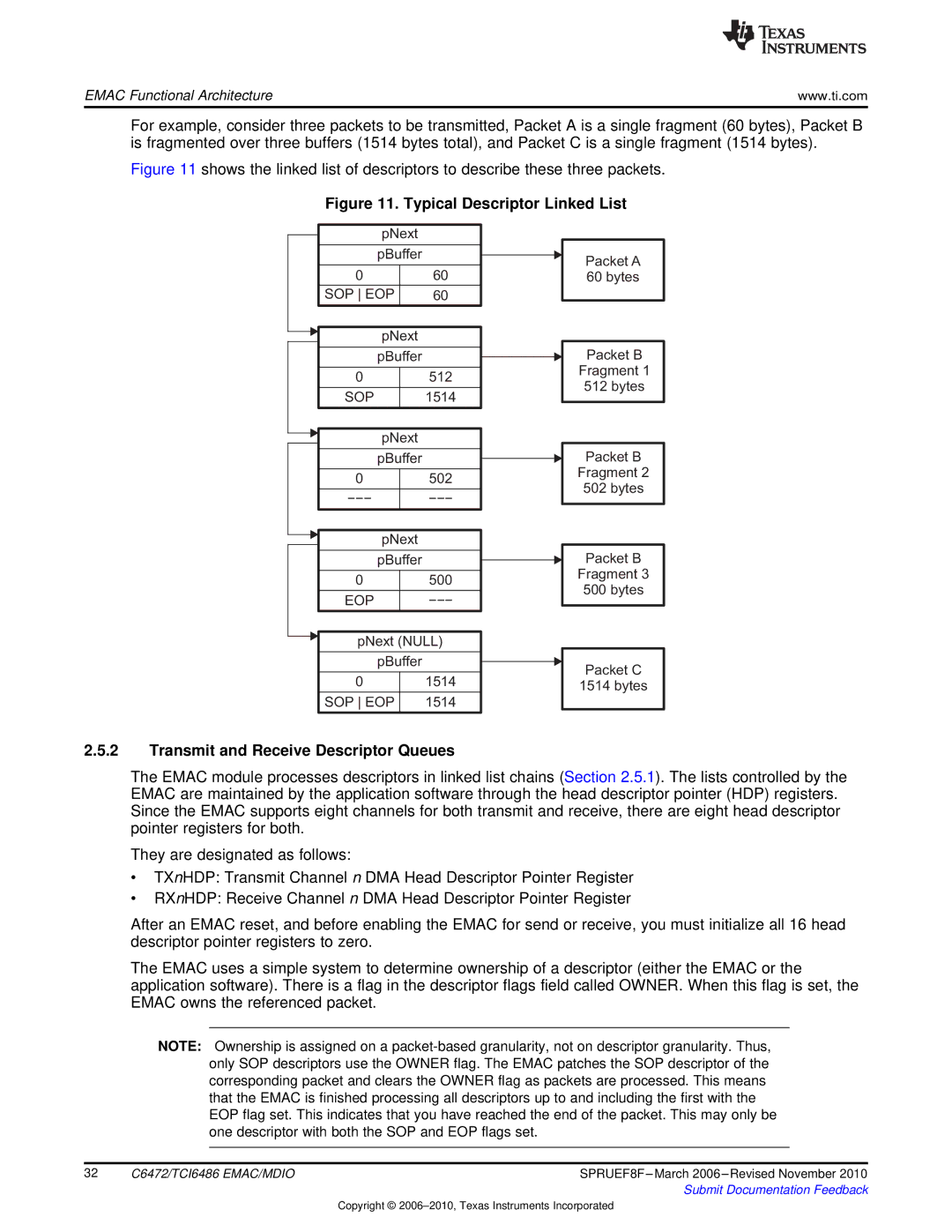

For example, consider three packets to be transmitted, Packet A is a single fragment (60 bytes), Packet B is fragmented over three buffers (1514 bytes total), and Packet C is a single fragment (1514 bytes).

Figure 11 shows the linked list of descriptors to describe these three packets.

Figure 11. Typical Descriptor Linked List

pNext

pBuffer

|

| 0 |

| 60 |

|

|

|

|

|

|

|

|

| SOP EOP |

| 60 |

|

|

|

|

|

|

|

|

| pNext |

|

| |

|

| pBuffer |

|

| |

|

|

|

| ||

|

|

|

|

|

|

|

| 0 |

| 512 |

|

|

|

|

|

|

|

|

| SOP |

| 1514 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| pNext |

|

| |

|

| pBuffer |

|

| |

|

|

|

| ||

|

|

|

|

|

|

|

| 0 |

| 502 |

|

|

|

|

|

|

|

|

| −−− |

| −−− |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| pNext |

|

| |

|

| pBuffer |

|

| |

|

|

|

| ||

|

|

|

|

|

|

|

| 0 |

| 500 |

|

|

|

|

|

|

|

|

| EOP |

| −−− |

|

|

|

|

|

| |

|

|

|

|

| |

|

| pNext (NULL) |

| ||

|

|

|

|

|

|

|

| pBuffer |

|

| |

|

|

|

| ||

|

|

|

|

|

|

|

| 0 |

| 1514 |

|

|

|

|

|

|

|

|

| SOP EOP |

| 1514 |

|

|

|

|

|

|

|

Packet A 60 bytes

Packet B

Fragment 1

512 bytes

Packet B

Fragment 2

502 bytes

Packet B

Fragment 3

500 bytes

Packet C

1514 bytes

2.5.2Transmit and Receive Descriptor Queues

The EMAC module processes descriptors in linked list chains (Section 2.5.1). The lists controlled by the EMAC are maintained by the application software through the head descriptor pointer (HDP) registers. Since the EMAC supports eight channels for both transmit and receive, there are eight head descriptor pointer registers for both.

They are designated as follows:

•TXnHDP: Transmit Channel n DMA Head Descriptor Pointer Register

•RXnHDP: Receive Channel n DMA Head Descriptor Pointer Register

After an EMAC reset, and before enabling the EMAC for send or receive, you must initialize all 16 head descriptor pointer registers to zero.

The EMAC uses a simple system to determine ownership of a descriptor (either the EMAC or the application software). There is a flag in the descriptor flags field called OWNER. When this flag is set, the EMAC owns the referenced packet.

NOTE: Ownership is assigned on a

32 | C6472/TCI6486 EMAC/MDIO | SPRUEF8F |

|

| Submit Documentation Feedback |

Copyright ©