Introduction | www.ti.com |

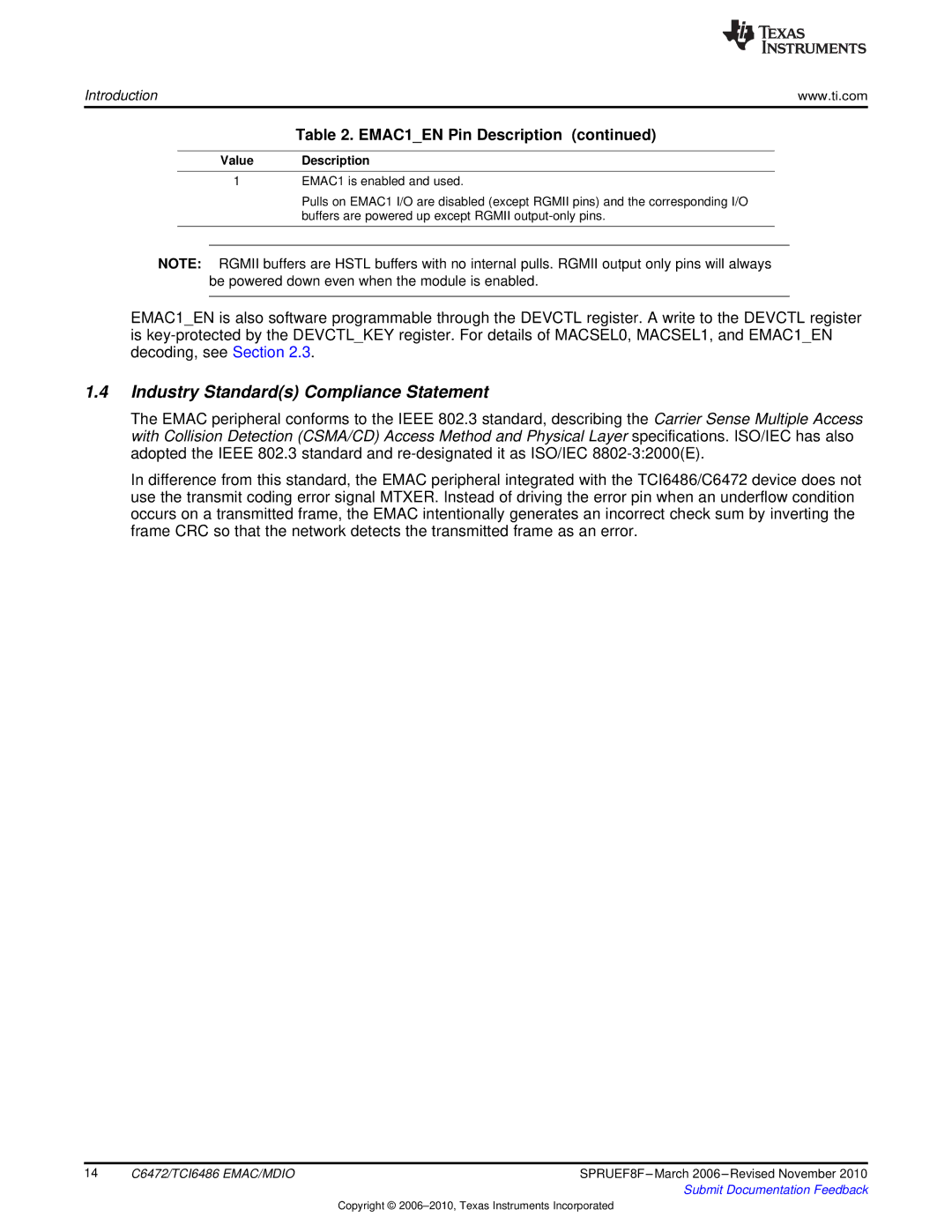

Table 2. EMAC1_EN Pin Description (continued)

Value Description

1EMAC1 is enabled and used.

Pulls on EMAC1 I/O are disabled (except RGMII pins) and the corresponding I/O buffers are powered up except RGMII

NOTE: RGMII buffers are HSTL buffers with no internal pulls. RGMII output only pins will always be powered down even when the module is enabled.

EMAC1_EN is also software programmable through the DEVCTL register. A write to the DEVCTL register is

1.4Industry Standard(s) Compliance Statement

The EMAC peripheral conforms to the IEEE 802.3 standard, describing the Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer specifications. ISO/IEC has also adopted the IEEE 802.3 standard and

In difference from this standard, the EMAC peripheral integrated with the TCI6486/C6472 device does not use the transmit coding error signal MTXER. Instead of driving the error pin when an underflow condition occurs on a transmitted frame, the EMAC intentionally generates an incorrect check sum by inverting the frame CRC so that the network detects the transmitted frame as an error.

14 | C6472/TCI6486 EMAC/MDIO | SPRUEF8F |

|

| Submit Documentation Feedback |

Copyright ©