www.ti.com | EMIC Module Registers |

3 EMIC Module Registers

3.1EW_INTCTL Registers

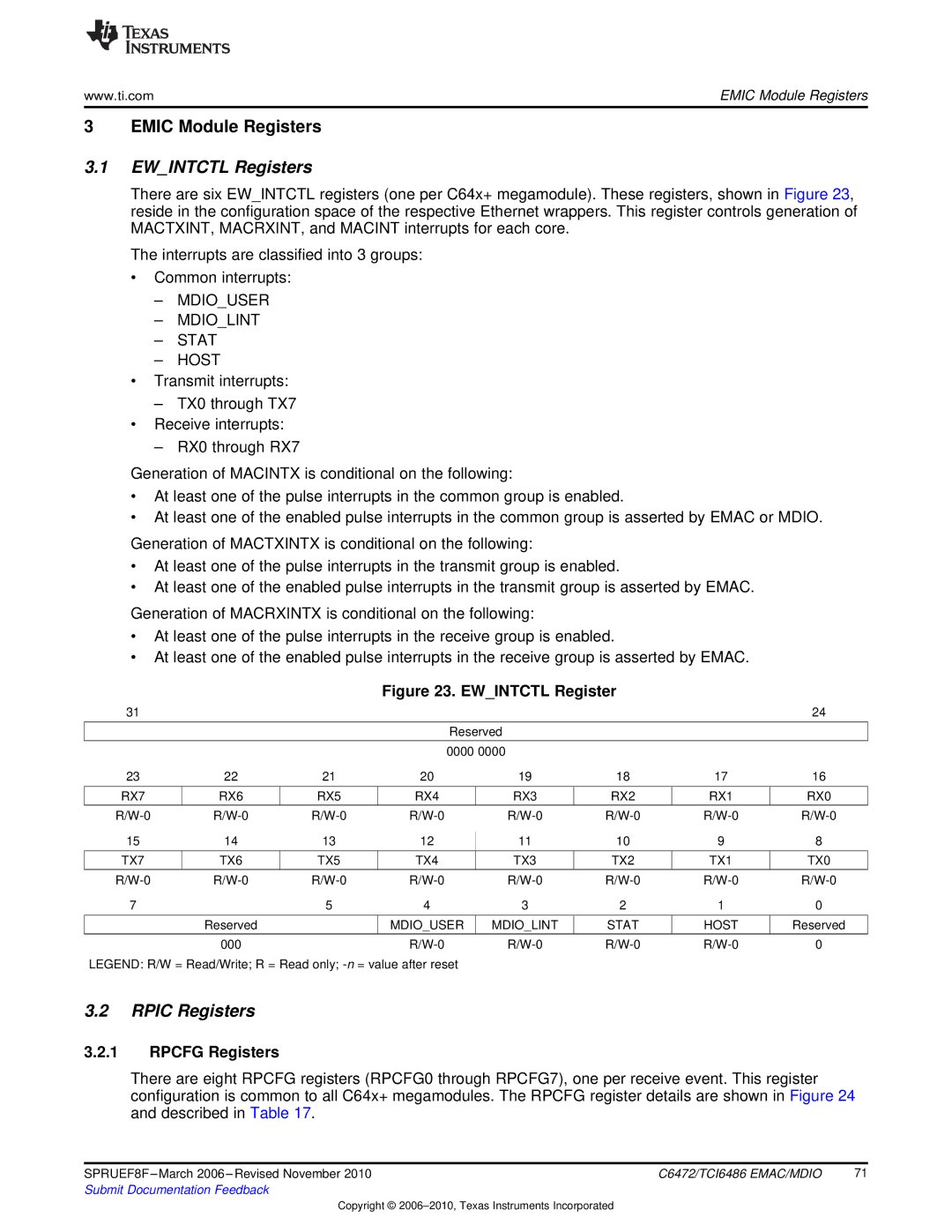

There are six EW_INTCTL registers (one per C64x+ megamodule). These registers, shown in Figure 23, reside in the configuration space of the respective Ethernet wrappers. This register controls generation of MACTXINT, MACRXINT, and MACINT interrupts for each core.

The interrupts are classified into 3 groups:

•Common interrupts:

–MDIO_USER

–MDIO_LINT

–STAT

–HOST

•Transmit interrupts:

–TX0 through TX7

•Receive interrupts:

–RX0 through RX7

Generation of MACINTX is conditional on the following:

•At least one of the pulse interrupts in the common group is enabled.

•At least one of the enabled pulse interrupts in the common group is asserted by EMAC or MDIO.

Generation of MACTXINTX is conditional on the following:

•At least one of the pulse interrupts in the transmit group is enabled.

•At least one of the enabled pulse interrupts in the transmit group is asserted by EMAC.

Generation of MACRXINTX is conditional on the following:

•At least one of the pulse interrupts in the receive group is enabled.

•At least one of the enabled pulse interrupts in the receive group is asserted by EMAC.

Figure 23. EW_INTCTL Register

31 |

|

|

|

|

|

| 24 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

| |

|

|

| 0000 0000 |

|

|

| |

23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|

|

|

|

|

|

|

|

RX7 | RX6 | RX5 | RX4 | RX3 | RX2 | RX1 | RX0 |

|

|

|

|

|

|

|

|

15 | 14 | 13 | 12 |

| 10 | 9 | 8 |

11 | |||||||

|

|

|

|

|

|

|

|

TX7 | TX6 | TX5 | TX4 | TX3 | TX2 | TX1 | TX0 |

7 |

| 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

| Reserved |

| MDIO_USER | MDIO_LINT | STAT | HOST | Reserved |

| 000 |

| 0 | ||||

LEGEND: R/W = Read/Write; R = Read only;

3.2RPIC Registers

3.2.1RPCFG Registers

There are eight RPCFG registers (RPCFG0 through RPCFG7), one per receive event. This register configuration is common to all C64x+ megamodules. The RPCFG register details are shown in Figure 24 and described in Table 17.

SPRUEF8F | C6472/TCI6486 EMAC/MDIO | 71 |

Submit Documentation Feedback |

|

|

Copyright ©