www.ti.com | Introduction |

The EMAC module provides an efficient interface between the TCI6486/C6472 core processor and the networked community. The EMAC supports

Each EMAC module has a communications port programming interface (CPPI) buffer manager to manage 8K of CPPI RAM. The EMAC uses four

The EMIC module associated with each EMAC takes a single set of interrupts from respective EMAC and common MDIO and creates six different sets of TX, RX, and common interrupts to six cores of the TCI6486/C6472 device. In addition, this module implements the interrupt pacing operation.

The control registers of the EMAC and MDIO modules are memory mapped into device memory space via the device configuration bus.

The MDIO module implements the 802.3 serial management interface to interrogate and control up to 32 Ethernet PHYs connected to the device, using a shared

MACSEL0[2:0] and MACSEL1[1:0] are device configuration pins used to select the MII interface for EMAC0 and EMAC1, respectively.

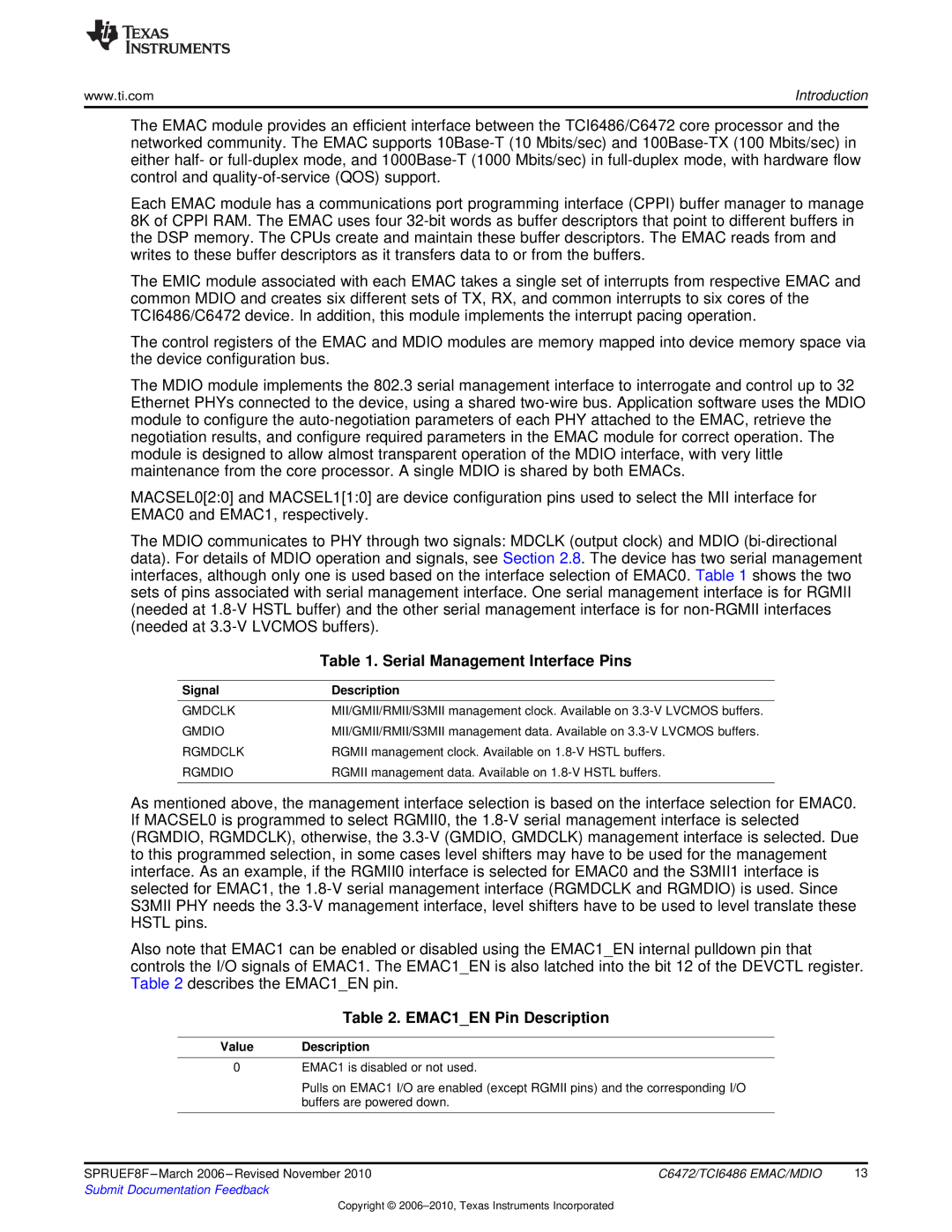

The MDIO communicates to PHY through two signals: MDCLK (output clock) and MDIO

| Table 1. Serial Management Interface Pins |

|

|

Signal | Description |

|

|

GMDCLK | MII/GMII/RMII/S3MII management clock. Available on |

GMDIO | MII/GMII/RMII/S3MII management data. Available on |

RGMDCLK | RGMII management clock. Available on |

RGMDIO | RGMII management data. Available on |

|

|

As mentioned above, the management interface selection is based on the interface selection for EMAC0. If MACSEL0 is programmed to select RGMII0, the

Also note that EMAC1 can be enabled or disabled using the EMAC1_EN internal pulldown pin that controls the I/O signals of EMAC1. The EMAC1_EN is also latched into the bit 12 of the DEVCTL register. Table 2 describes the EMAC1_EN pin.

Table 2. EMAC1_EN Pin Description

Value Description

0EMAC1 is disabled or not used.

Pulls on EMAC1 I/O are enabled (except RGMII pins) and the corresponding I/O buffers are powered down.

SPRUEF8F | C6472/TCI6486 EMAC/MDIO | 13 |

Submit Documentation Feedback |

|

|

Copyright ©