EMAC Port Registers | www.ti.com |

5.10 Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR)

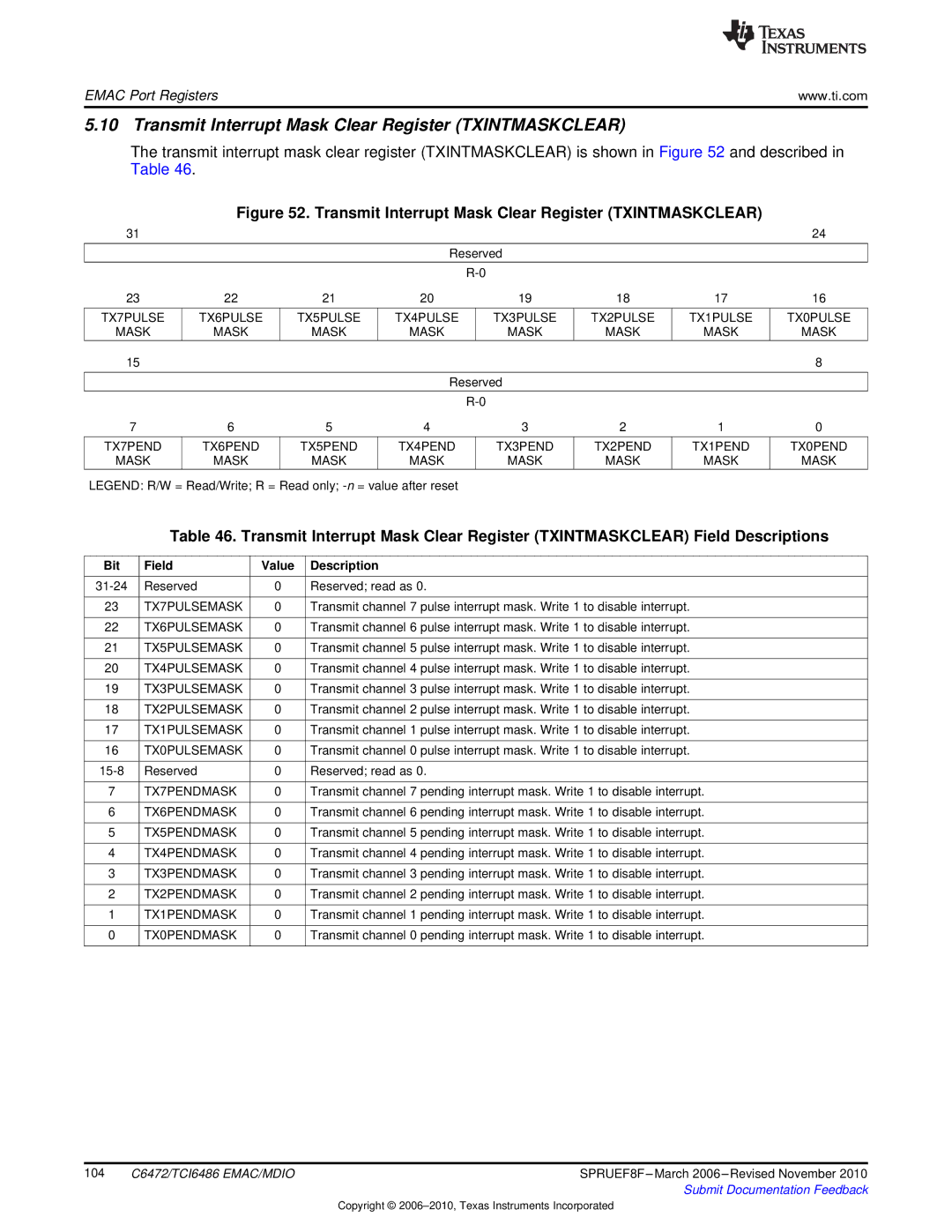

The transmit interrupt mask clear register (TXINTMASKCLEAR) is shown in Figure 52 and described in Table 46.

Figure 52. Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR)

31 |

|

|

|

|

|

|

| 24 |

|

|

| Reserved |

|

|

| ||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| ||

23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

|

|

|

|

|

|

|

|

|

TX7PULSE | TX6PULSE | TX5PULSE | TX4PULSE |

| TX3PULSE | TX2PULSE | TX1PULSE | TX0PULSE |

MASK | MASK | MASK | MASK |

| MASK | MASK | MASK | MASK |

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

| 8 |

|

|

|

|

|

|

| ||

|

|

| Reserved |

|

|

| ||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| ||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|

|

|

|

|

|

|

|

|

TX7PEND | TX6PEND | TX5PEND | TX4PEND |

| TX3PEND | TX2PEND | TX1PEND | TX0PEND |

MASK | MASK | MASK | MASK |

| MASK | MASK | MASK | MASK |

LEGEND: R/W = Read/Write; R = Read only;

Table 46. Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved; read as 0. | |

|

|

|

|

23 | TX7PULSEMASK | 0 | Transmit channel 7 pulse interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

22 | TX6PULSEMASK | 0 | Transmit channel 6 pulse interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

21 | TX5PULSEMASK | 0 | Transmit channel 5 pulse interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

20 | TX4PULSEMASK | 0 | Transmit channel 4 pulse interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

19 | TX3PULSEMASK | 0 | Transmit channel 3 pulse interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

18 | TX2PULSEMASK | 0 | Transmit channel 2 pulse interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

17 | TX1PULSEMASK | 0 | Transmit channel 1 pulse interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

16 | TX0PULSEMASK | 0 | Transmit channel 0 pulse interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

Reserved | 0 | Reserved; read as 0. | |

|

|

|

|

7 | TX7PENDMASK | 0 | Transmit channel 7 pending interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

6 | TX6PENDMASK | 0 | Transmit channel 6 pending interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

5 | TX5PENDMASK | 0 | Transmit channel 5 pending interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

4 | TX4PENDMASK | 0 | Transmit channel 4 pending interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

3 | TX3PENDMASK | 0 | Transmit channel 3 pending interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

2 | TX2PENDMASK | 0 | Transmit channel 2 pending interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

1 | TX1PENDMASK | 0 | Transmit channel 1 pending interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

0 | TX0PENDMASK | 0 | Transmit channel 0 pending interrupt mask. Write 1 to disable interrupt. |

|

|

|

|

104 | C6472/TCI6486 EMAC/MDIO | SPRUEF8F |

|

| Submit Documentation Feedback |

Copyright ©