EMAC Functional Architecture | www.ti.com |

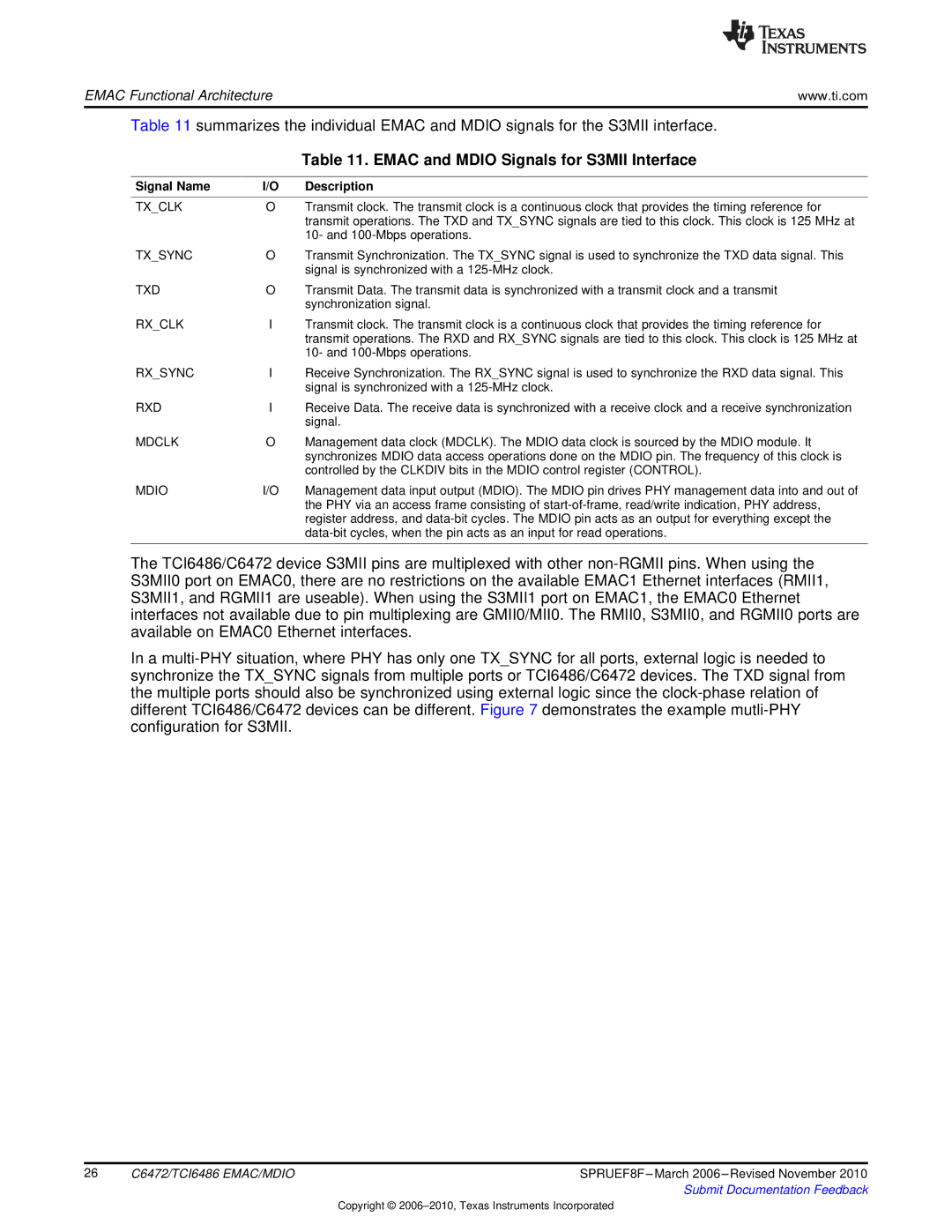

Table 11 summarizes the individual EMAC and MDIO signals for the S3MII interface.

|

| Table 11. EMAC and MDIO Signals for S3MII Interface |

|

|

|

Signal Name | I/O | Description |

|

|

|

TX_CLK | O | Transmit clock. The transmit clock is a continuous clock that provides the timing reference for |

|

| transmit operations. The TXD and TX_SYNC signals are tied to this clock. This clock is 125 MHz at |

|

| 10- and |

TX_SYNC | O | Transmit Synchronization. The TX_SYNC signal is used to synchronize the TXD data signal. This |

|

| signal is synchronized with a |

TXD | O | Transmit Data. The transmit data is synchronized with a transmit clock and a transmit |

|

| synchronization signal. |

RX_CLK | I | Transmit clock. The transmit clock is a continuous clock that provides the timing reference for |

|

| transmit operations. The RXD and RX_SYNC signals are tied to this clock. This clock is 125 MHz at |

|

| 10- and |

RX_SYNC | I | Receive Synchronization. The RX_SYNC signal is used to synchronize the RXD data signal. This |

|

| signal is synchronized with a |

RXD | I | Receive Data. The receive data is synchronized with a receive clock and a receive synchronization |

|

| signal. |

MDCLK | O | Management data clock (MDCLK). The MDIO data clock is sourced by the MDIO module. It |

|

| synchronizes MDIO data access operations done on the MDIO pin. The frequency of this clock is |

|

| controlled by the CLKDIV bits in the MDIO control register (CONTROL). |

MDIO | I/O | Management data input output (MDIO). The MDIO pin drives PHY management data into and out of |

|

| the PHY via an access frame consisting of |

|

| register address, and |

|

| |

|

|

|

The TCI6486/C6472 device S3MII pins are multiplexed with other

In a

26 | C6472/TCI6486 EMAC/MDIO | SPRUEF8F |

|

| Submit Documentation Feedback |

Copyright ©