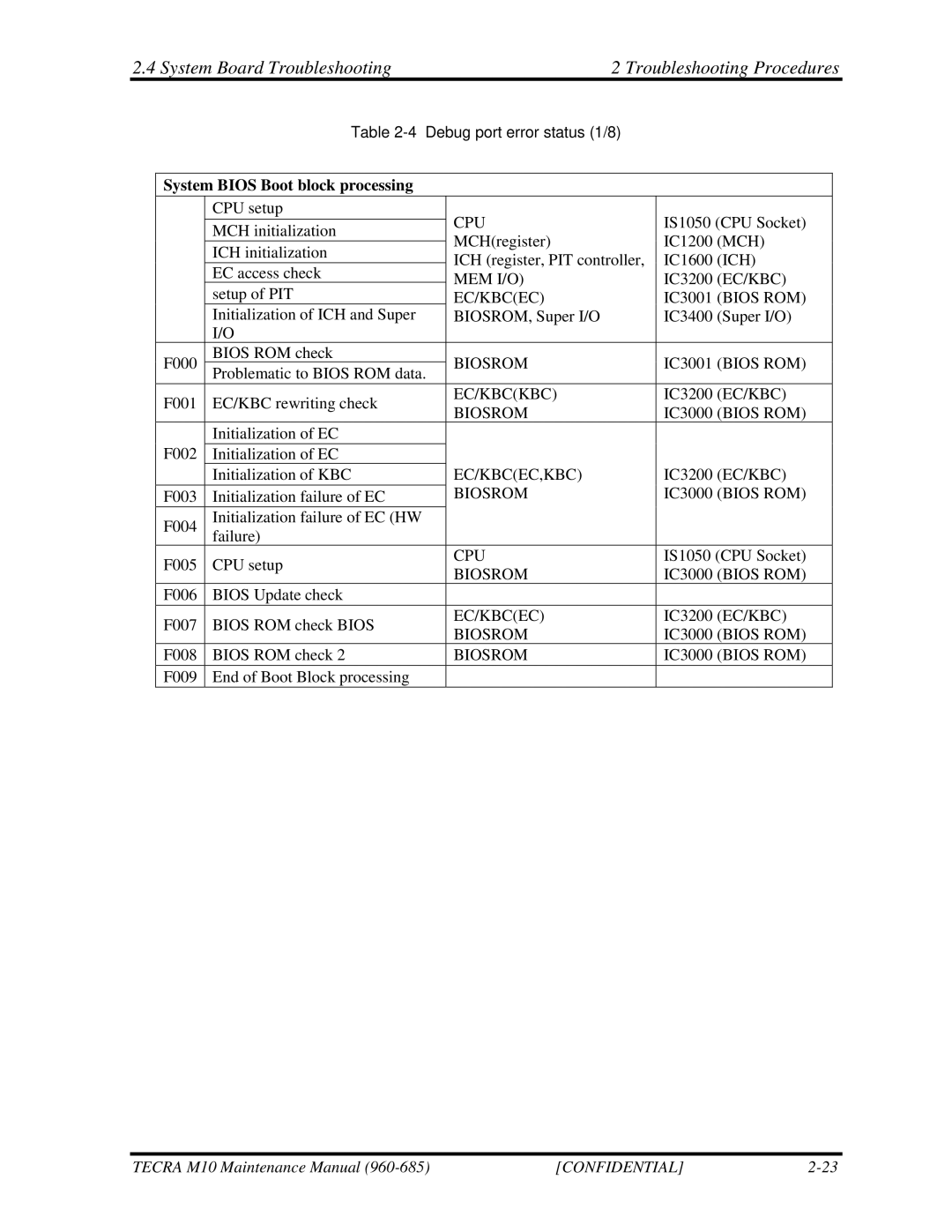

2.4 System Board Troubleshooting | 2 Troubleshooting Procedures |

Table

System BIOS Boot block processing

| CPU setup | CPU | IS1050 (CPU Socket) | |

| MCH initialization | |||

| MCH(register) | IC1200 (MCH) | ||

| ICH initialization | |||

| ICH (register, PIT controller, | IC1600 (ICH) | ||

| EC access check | |||

| MEM I/O) | IC3200 (EC/KBC) | ||

| setup of PIT | |||

| EC/KBC(EC) | IC3001 (BIOS ROM) | ||

| Initialization of ICH and Super | BIOSROM, Super I/O | IC3400 (Super I/O) | |

| I/O |

|

| |

F000 | BIOS ROM check | BIOSROM | IC3001 (BIOS ROM) | |

Problematic to BIOS ROM data. | ||||

F001 | EC/KBC rewriting check | EC/KBC(KBC) | IC3200 (EC/KBC) | |

BIOSROM | IC3000 (BIOS ROM) | |||

|

| |||

F002 | Initialization of EC |

|

| |

Initialization of EC | EC/KBC(EC,KBC) | IC3200 (EC/KBC) | ||

| Initialization of KBC | |||

F003 | Initialization failure of EC | BIOSROM | IC3000 (BIOS ROM) | |

F004 | Initialization failure of EC (HW |

|

| |

| failure) |

|

| |

F005 | CPU setup | CPU | IS1050 (CPU Socket) | |

BIOSROM | IC3000 (BIOS ROM) | |||

|

| |||

F006 | BIOS Update check |

|

| |

F007 | BIOS ROM check BIOS | EC/KBC(EC) | IC3200 (EC/KBC) | |

BIOSROM | IC3000 (BIOS ROM) | |||

|

| |||

F008 | BIOS ROM check 2 | BIOSROM | IC3000 (BIOS ROM) | |

F009 | End of Boot Block processing |

|

|

TECRA M10 Maintenance Manual | [CONFIDENTIAL] |