Reset, Interrupts, Exceptions, and Break

R

•Unaligned Exception

The unaligned exception is caused by a word access where the address to the data bus has bits 30 or 31 set, or a

•Divide by Zero Exception

The

•FPU Exception

An FPU exception is caused by an underflow, overflow,

♦Underflow occurs when the result is denormalized.

♦Overflow occurs when the result is

♦The

♦Illegal operation is caused by a signaling NaN operand or by illegal infinite or zero operand combinations.

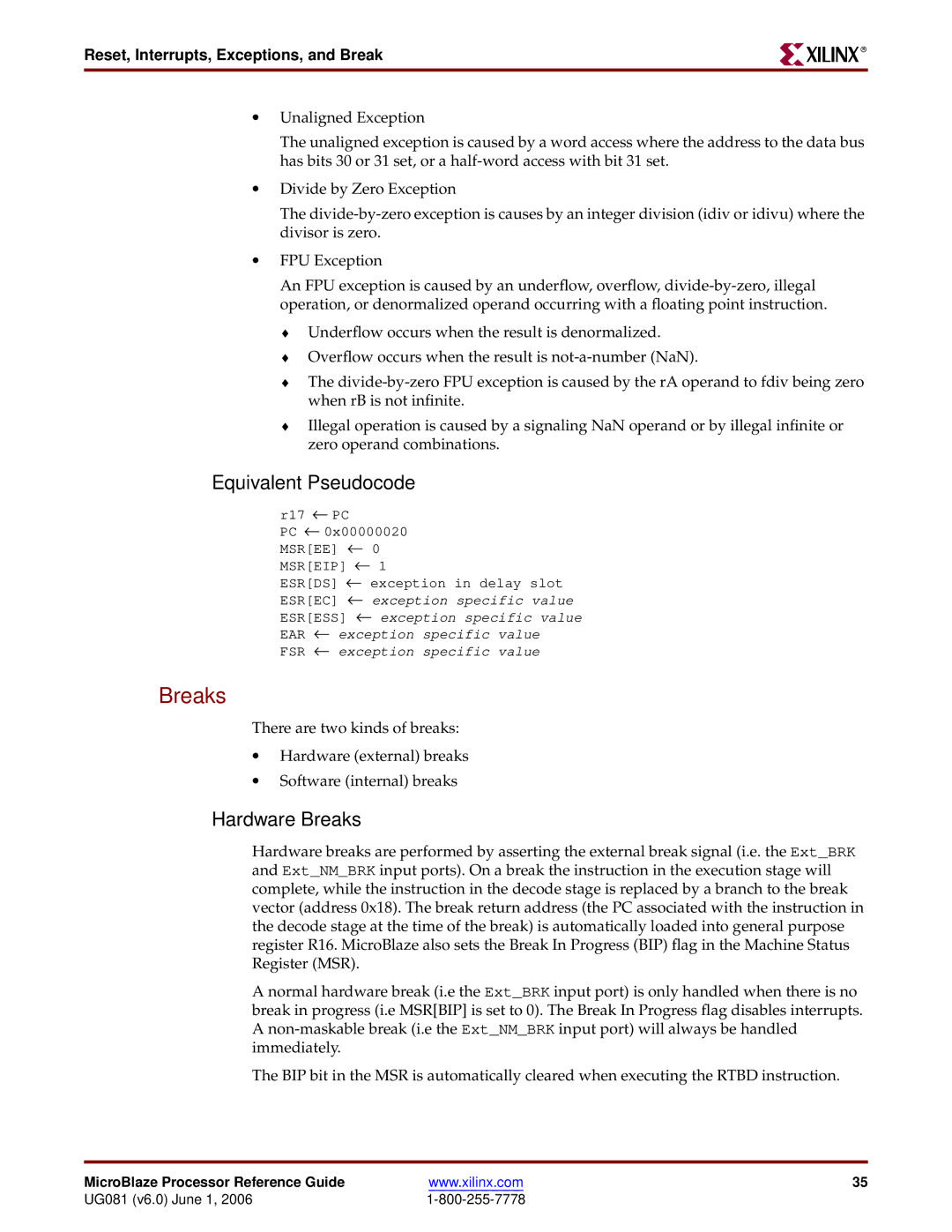

Equivalent Pseudocode

r17 ← PC

PC ← 0x00000020 MSR[EE] ← 0 MSR[EIP] ← 1

ESR[DS] ← exception in delay slot

ESR[EC] ← exception specific value

ESR[ESS] ← exception specific value

EAR ← exception specific value

FSR ← exception specific value

Breaks

There are two kinds of breaks:

•Hardware (external) breaks

•Software (internal) breaks

Hardware Breaks

Hardware breaks are performed by asserting the external break signal (i.e. the Ext_BRK and Ext_NM_BRK input ports). On a break the instruction in the execution stage will complete, while the instruction in the decode stage is replaced by a branch to the break vector (address 0x18). The break return address (the PC associated with the instruction in the decode stage at the time of the break) is automatically loaded into general purpose register R16. MicroBlaze also sets the Break In Progress (BIP) flag in the Machine Status Register (MSR).

A normal hardware break (i.e the Ext_BRK input port) is only handled when there is no break in progress (i.e MSR[BIP] is set to 0). The Break In Progress flag disables interrupts. A

The BIP bit in the MSR is automatically cleared when executing the RTBD instruction.

MicroBlaze Processor Reference Guide | www.xilinx.com | 35 |

UG081 (v6.0) June 1, 2006 |

|