Floating Point Unit (FPU)

R

Format

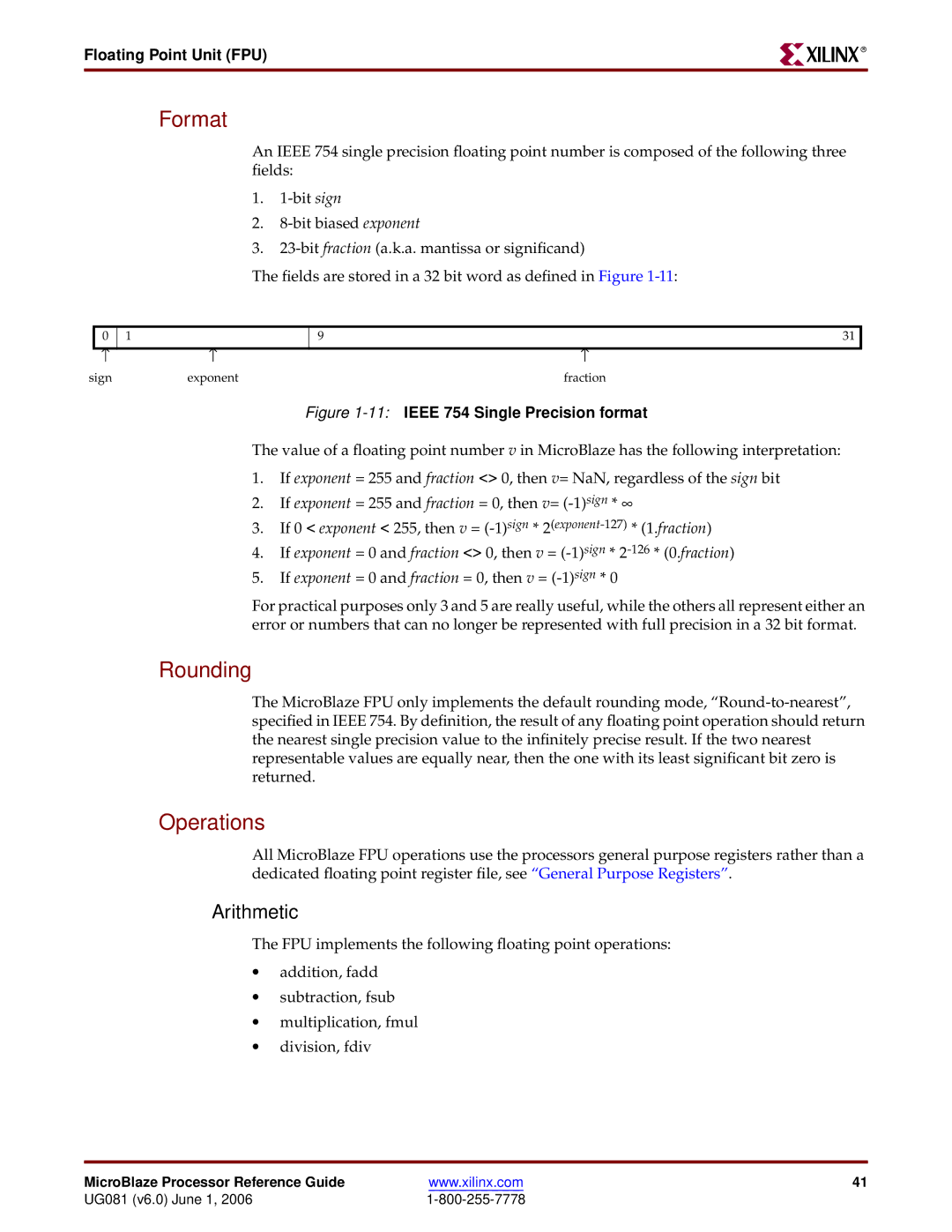

An IEEE 754 single precision floating point number is composed of the following three fields:

1.

2.

3.

The fields are stored in a 32 bit word as defined in Figure

0

↑

1

↑

9 | 31 |

↑

sign | exponent | fraction |

Figure 1-11: IEEE 754 Single Precision format

The value of a floating point number v in MicroBlaze has the following interpretation:

1.If exponent = 255 and fraction <> 0, then v= NaN, regardless of the sign bit

2.If exponent = 255 and fraction = 0, then v=

3.If 0 < exponent < 255, then v =

4.If exponent = 0 and fraction <> 0, then v =

5.If exponent = 0 and fraction = 0, then v =

For practical purposes only 3 and 5 are really useful, while the others all represent either an error or numbers that can no longer be represented with full precision in a 32 bit format.

Rounding

The MicroBlaze FPU only implements the default rounding mode,

Operations

All MicroBlaze FPU operations use the processors general purpose registers rather than a dedicated floating point register file, see “General Purpose Registers”.

Arithmetic

The FPU implements the following floating point operations:

•addition, fadd

•subtraction, fsub

•multiplication, fmul

•division, fdiv

MicroBlaze Processor Reference Guide | www.xilinx.com | 41 |

UG081 (v6.0) June 1, 2006 |

|