Instructions

bs | Barrel Shift |

|

|

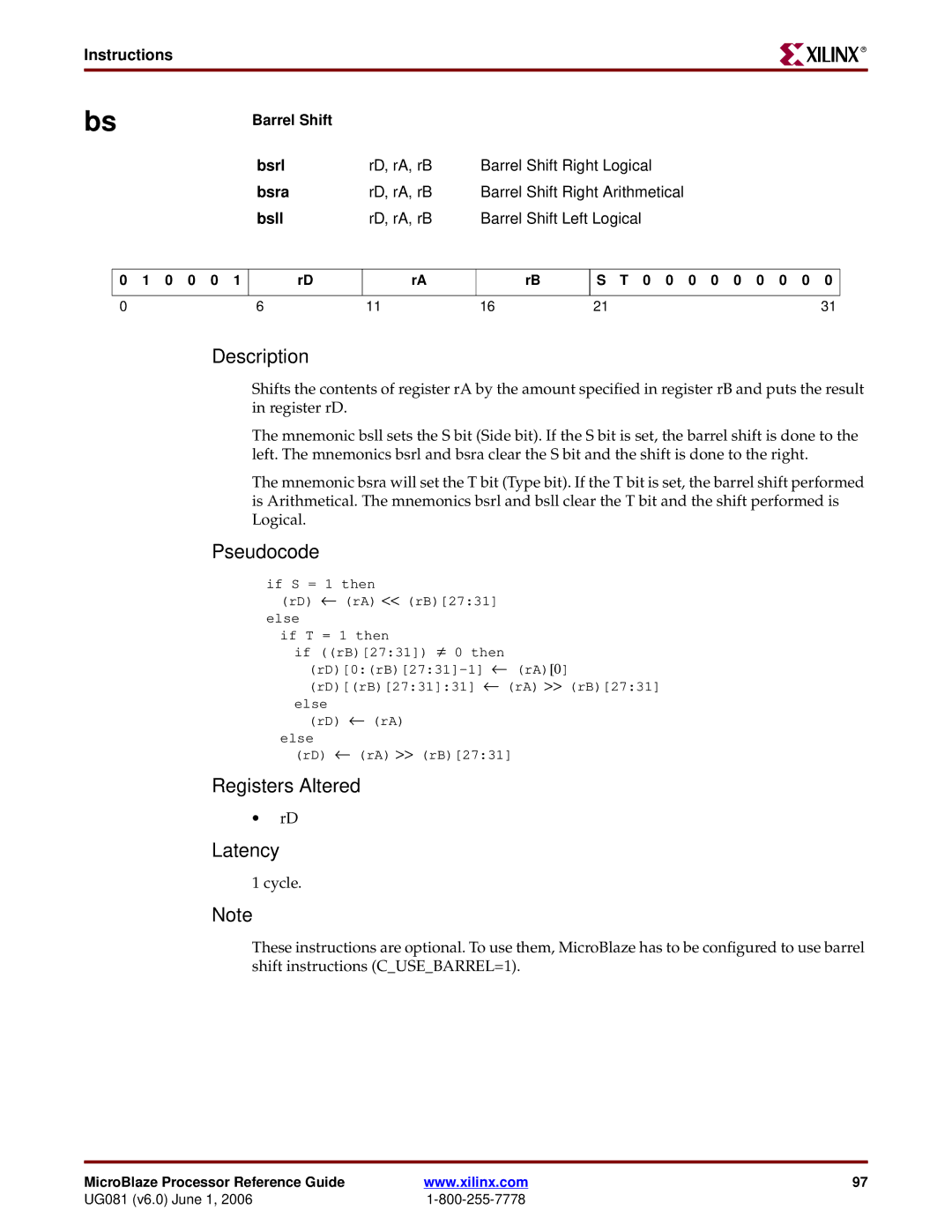

| bsrl | rD, rA, rB | Barrel Shift Right Logical |

| bsra | rD, rA, rB | Barrel Shift Right Arithmetical |

| bsll | rD, rA, rB | Barrel Shift Left Logical |

R

0 1 0 0 0 1

rD

rA

rB

S T 0 0 0 0 0 0 0 0 0

0 | 6 | 11 | 16 | 21 | 31 |

Description

Shifts the contents of register rA by the amount specified in register rB and puts the result in register rD.

The mnemonic bsll sets the S bit (Side bit). If the S bit is set, the barrel shift is done to the left. The mnemonics bsrl and bsra clear the S bit and the shift is done to the right.

The mnemonic bsra will set the T bit (Type bit). If the T bit is set, the barrel shift performed is Arithmetical. The mnemonics bsrl and bsll clear the T bit and the shift performed is Logical.

Pseudocode

if S = 1 then |

|

|

| |

(rD) ← | (rA) << | (rB)[27:31] |

|

|

else |

|

|

|

|

if T = 1 then |

|

|

| |

if ((rB)[27:31]) ≠ 0 then |

|

| ||

(rA)[0 | ] | |||

(rD)[(rB)[27:31]:31] ← | (rA) >> | (rB)[27:31] | ||

else |

|

|

|

|

(rD) ← (rA) |

|

|

| |

else |

|

|

|

|

(rD) ← | (rA) >> | (rB)[27:31] |

| |

Registers Altered

•rD

Latency

1 cycle.

Note

These instructions are optional. To use them, MicroBlaze has to be configured to use barrel shift instructions (C_USE_BARREL=1).

MicroBlaze Processor Reference Guide | www.xilinx.com | 97 |

UG081 (v6.0) June 1, 2006 |

|