MicroBlaze Processor Reference Guide

UG081 v6.0 June 1

MicroBlaze Processor Reference Guide

MicroBlaze Processor Reference Guide UG081 v6.0 June 1

Date Version Revision

UG081 v6.0 June 1

Preface About This Guide

MicroBlaze Application Binary Interface

Manual Contents

Additional Resources

Conventions

Typographical

Online Document

Conventions Meaning or Use Example

UG081 v6.0 June 1

Features

Overview

MicroBlaze Architecture

Version Status Deprecated Active

Data Types and Endianness

Instructions

MSR

ESR

EAR

FSR

Op1 if cond else op2

MicroBlaze Processor Reference Guide

MicroBlaze Processor Reference Guide UG081 v6.0 June 1

MicroBlaze Processor Reference Guide

MicroBlaze Processor Reference Guide UG081 v6.0 June 1

Registers

General Purpose Registers

Special Purpose Registers

Program Counter PC

Registers

8Program Counter PC Bits Name Description Reset Value

Machine Status Register MSR

9Machine Status Register MSR Bits Name Description

PVR

EIP

DCE

ICE

FSL

Buslock Enable

Exception Address Register EAR

Exception Status Register ESR

ESS

Branch Target Register BTR

Source/Destination Register

Floating Point Status Register FSR

Processor Version Register PVR

CFG

Cusebarrel

DIV

Cusediv

Cdebugenabled

OP0EXEC

Unexec

Cunalignedexception

Icll

Cicachelinelen

Icbs

Ccachebytesize

Cresetmsr

Pipeline Architecture

Arch

Rstmsr

Memory Architecture

Delay Slots

Branches

Reset, Interrupts, Exceptions, and Break

Reset, Interrupts, Exceptions, and Break

Reset

Hardware Exceptions

Equivalent Pseudocode

Exception Causes

Breaks

Hardware Breaks

Interrupt

User Vector Exception

Software Breaks

Latency

Instruction Cache

Overview

General Instruction Cache Functionality

Instruction Cache

Data Cache

Instruction Cache Operation

Instruction Cache Software Support

MSR Bit

Data Cache Operation

General Data Cache Functionality

Data Cache

Data Cache Software Support

Floating Point Unit FPU

WDC Instruction

Format

Rounding

Operations

Arithmetic

Hardware Acceleration using FSL

Fast Simplex Link FSL

Exceptions

Comparison

Debug Overview

Debug and Trace

Trace Overview

MicroBlaze Architecture

MicroBlaze I/O Overview

Ilmb

Ixcl

Dxcl

MicroBlaze Signal Interface Description

Dmrnw Dopb

Imrnw Iopb

DAS Dlmb

IAS Ilmb

Mfsl

On-Chip Peripheral Bus OPB Interface Description

Ixclm

Dxcls

Dxclm

LMB Signal Interface

ByteEnable03

Local Memory Bus LMB Interface Description

Addr031

DataWrite031

ReadStrobe

WriteStrobe

DataRead031

Generic Write Operation

LMB Transactions

Generic Read Operation

Back-to-Back Write Operation

Single Cycle Back-to-Back Read Operation

Back-to-Back Mixed Read/Write Operation

BE0 BE1 BE2

RD1623 RD2431

Read and Write Data Steering

RD07 RD815 RD1623 RD2431

Slave FSL Signal Interface

Master FSL Signal Interface

Fast Simplex Link FSL Interface Description

Xilinx CacheLink XCL Interface Description

FSL Transactions

FSL BUS Write Operation

FSL BUS Read Operation

CacheLink Signal Interface

CacheLink Transactions

Data Cache Read Miss

Instruction Cache Read Miss

Data Cache Write

Debug Interface Description

Trace Interface Description

Debug Interface Description

MDM

MicroBlaze Processor Reference Guide

MicroBlaze Core Configurability

11 Type of Trace Exception TraceExceptionKind Description

Values Assigned Type

Cusepcmpinstr

Cusemsrinstr

Pcmpne Cunalignedexception

Cnumberofrdaddrbrk

Cicacheusefsl

Ffff

Cdcacheusefsl

Scope

Data Types

MicroBlaze Application Binary Interface

Register Usage Conventions

2Register usage conventions Type Enforcement Purpose

Stack Convention

Stack Convention

High Memory Low Memory Func

Memory Model

Interrupt and Exception Handling

Summary

1Symbol notation Meaning

Notation

Formats

Type a

Type B

Opcode Destination Reg Source Reg a Immediate Value

Description

Add

Registers Altered

Addi

Registers Altered Latency

RD, rA, rB

Andi

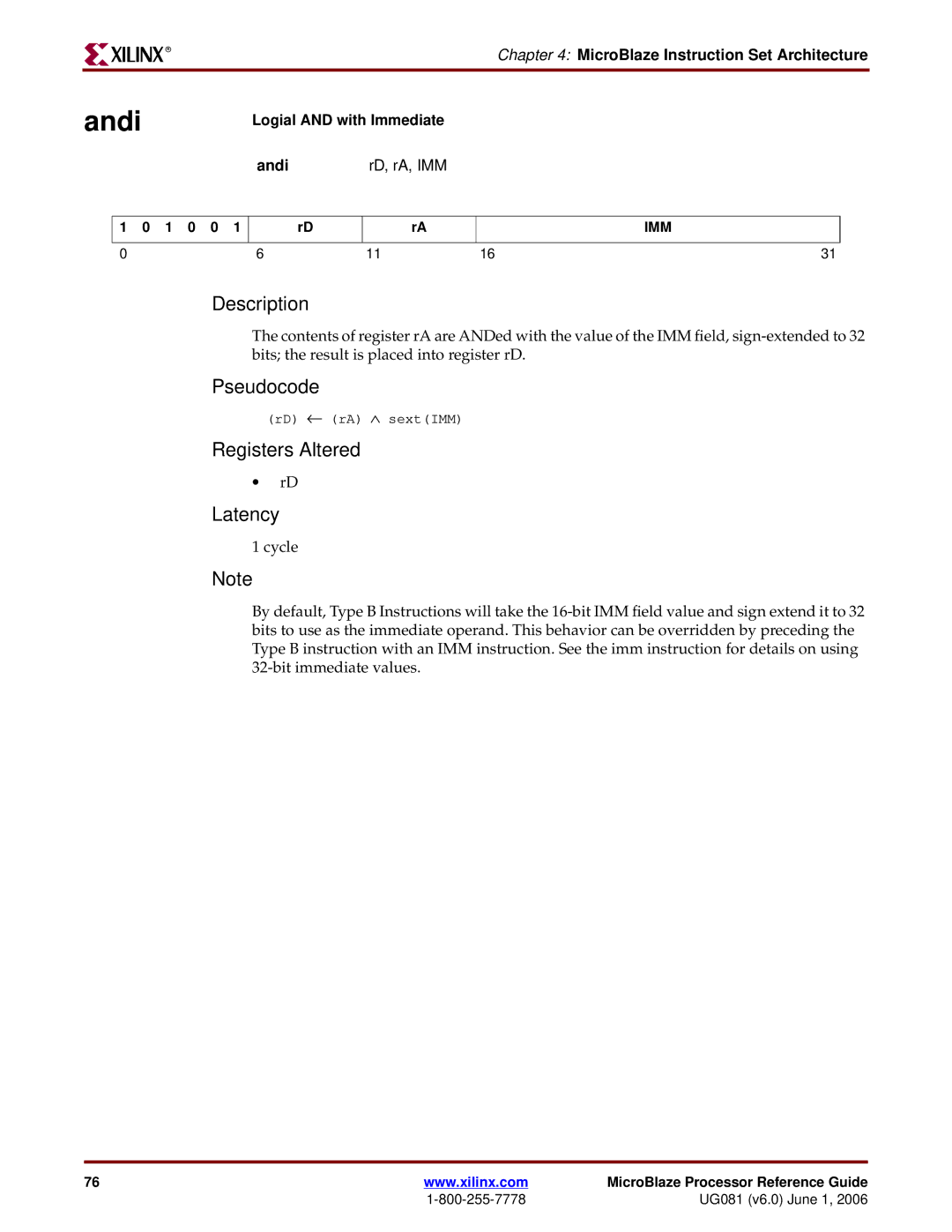

Logial and with Immediate Andi RD, rA, IMM

Logical and not

Andn

Andn RD, rA, rB

Andni

Logical and not with Immediate Andni RD, rA, IMM

Branch if Equal Beq

Beq

Beqd

Branch Immediate if Equal Beqi

Beqi

Beqid

Branch if Greater or Equal Bge

Bge

Bged

Branch Immediate if Greater or Equal Bgei

Bgei

Bgeid

Branch if Greater Than Bgt

Bgt

Bgtd

Branch Immediate if Greater Than Bgti

Bgti

Bgtid

Branch if Less or Equal Ble

Ble

Bled

Branch Immediate if Less or Equal Blei

Blei

Bleid

Blt

Branch if Less Than Blt

Blti

Blti

Bltid

Branch if Not Equal Bne

Bne

Bned

Branch Immediate if Not Equal Bnei

Bnei

Bneid

Instructions Unconditional Branch

Bra

Brd

Brad

MicroBlaze Instruction Set Architecture

Bri

MicroBlaze Instruction Set Architecture

Instructions BrkBreak RD, rB

Msrbip

Brki

Break Immediate Brki RD, IMM

Bsra

Instructions Barrel Shift Bsrl

Bsll

Bsi

Barrel Shift Immediate Bsrli

Bsrai

Bslli

Integer Compare Cmp

Cmp

Cmpu

Floating Point Arithmetic Add Fadd

Fadd

Esrec FSRIO,UF,OF,DO

Reverse Floating Point Arithmetic Subtraction

Frsub

Frsub RD, rA, rB Reverse subtract

Fmul

Floating Point Arithmetic Multiplication Fmul

Fdiv

Floating Point Arithmetic Division

Fdiv RD, rA, rB Divide

Esrec FSRIO,UF,OF,DO,DZ

Fcmp

Esrec FSRIO,DO

Get

Get from fsl interface

Nget

Cget

Integer Divide Idiv

Idiv

Idivu

Imm

Immediate ImmIMM

Load Byte Unsigned

Lbu

Lbu RD, rA, rB

Lbui

Load Byte Unsigned Immediate Lbui RD, rA, IMM

Lhu

Lhu RD, rA, rB

Lhui

Load Halfword Unsigned Immediate Lhui RD, rA, IMM

Load Word

Lwi

Load Word Immediate Lwi RD, rA, IMM

Mfs

Mfs RD, rS

Msrclr

Read MSR and clear bits in MSR Msrclr RD, Imm

Msrset

Msrset RD, Imm

Mts

Move To Special Purpose Register Mts RS, rA

Instructions Mul Multiply RD, rA, rB

Muli

Multiply Immediate Muli RD, rA, IMM

Logical or

Ori

Logical or with Immediate Ori RD, rA, IMM

Pcmpbf

Pattern Compare Byte Find Pcmpbf

Pcmpeq

Pattern Compare Equal Pcmpeq

Pcmpne

Pattern Compare Not Equal Pcmpne

Put

Put to fsl interface

Nput

Cput

Rsub

Arithmetic Reverse Subtract Rsub

Rsubc

Rsubk

Rsubi

Arithmetic Reverse Subtract Immediate Rsubi

Rsubic

Rsubik

Return from Break

Rtbd

Rtbd RA, IMM

Return from Interrupt Rtid RA, IMM

Rtid

Msrie

Return from Exception Rted RA, IMM

Rted

Msree Msreip ESR

Rtsd

Return from Subroutine Rtsd RA, IMM

None

Sbi

Store Byte Immediate Sbi RD, rA, IMM

Sext16

Sext16 RD, rA

Sign Extend Byte

Sext8

Sext8 RD, rA

Instructions Store Halfword RD, rA, rB

Shi

Store Halfword Immediate Shi RD, rA, IMM

Sra

Sra RD, rA

Src

Shift Right with Carry Src RD, rA

Shift Right Logical

Srl

Srl RD, rA

Addr ← rA + rB Addr3031 ← MemAddr ← rD031

Register Altered

Store Word Immediate Swi RD, rA, IMM

Wdc

Write to Data Cache

Wic

Xor

Logical Exclusive or Xor RD, rA, rB

Logical Exclusive or with Immediate

Xori

Xori RA, rD, IMM

148