Instructions

add | Arithmetic Add |

|

|

| add | rD, rA, rB | Add |

| addc | rD, rA, rB | Add with Carry |

| addk | rD, rA, rB | Add and Keep Carry |

| addkc | rD, rA, rB | Add with Carry and Keep Carry |

R

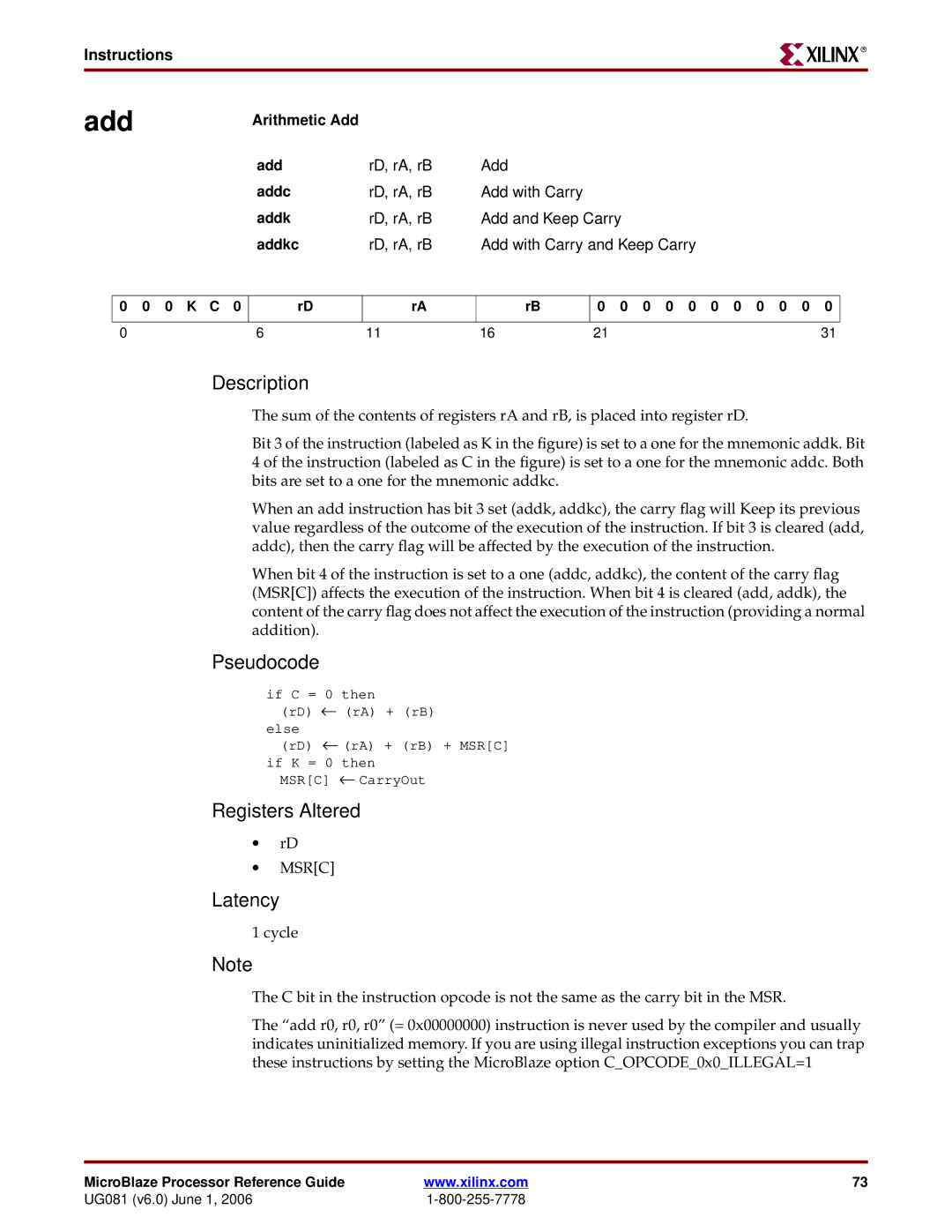

0 0 0 K C 0

rD

rA

rB

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 6 | 11 | 16 | 21 | 31 |

Description

The sum of the contents of registers rA and rB, is placed into register rD.

Bit 3 of the instruction (labeled as K in the figure) is set to a one for the mnemonic addk. Bit 4 of the instruction (labeled as C in the figure) is set to a one for the mnemonic addc. Both bits are set to a one for the mnemonic addkc.

When an add instruction has bit 3 set (addk, addkc), the carry flag will Keep its previous value regardless of the outcome of the execution of the instruction. If bit 3 is cleared (add, addc), then the carry flag will be affected by the execution of the instruction.

When bit 4 of the instruction is set to a one (addc, addkc), the content of the carry flag (MSR[C]) affects the execution of the instruction. When bit 4 is cleared (add, addk), the content of the carry flag does not affect the execution of the instruction (providing a normal addition).

Pseudocode

if C = 0 then

(rD) ← (rA) + (rB) else

(rD) ← (rA) + (rB) + MSR[C] if K = 0 then

MSR[C] ← CarryOut

Registers Altered

•rD

•MSR[C]

Latency

1 cycle

Note

The C bit in the instruction opcode is not the same as the carry bit in the MSR.

The “add r0, r0, r0” (= 0x00000000) instruction is never used by the compiler and usually indicates uninitialized memory. If you are using illegal instruction exceptions you can trap these instructions by setting the MicroBlaze option C_OPCODE_0x0_ILLEGAL=1

MicroBlaze Processor Reference Guide | www.xilinx.com | 73 |

UG081 (v6.0) June 1, 2006 |

|