MicroBlaze Core Configurability

Table

R

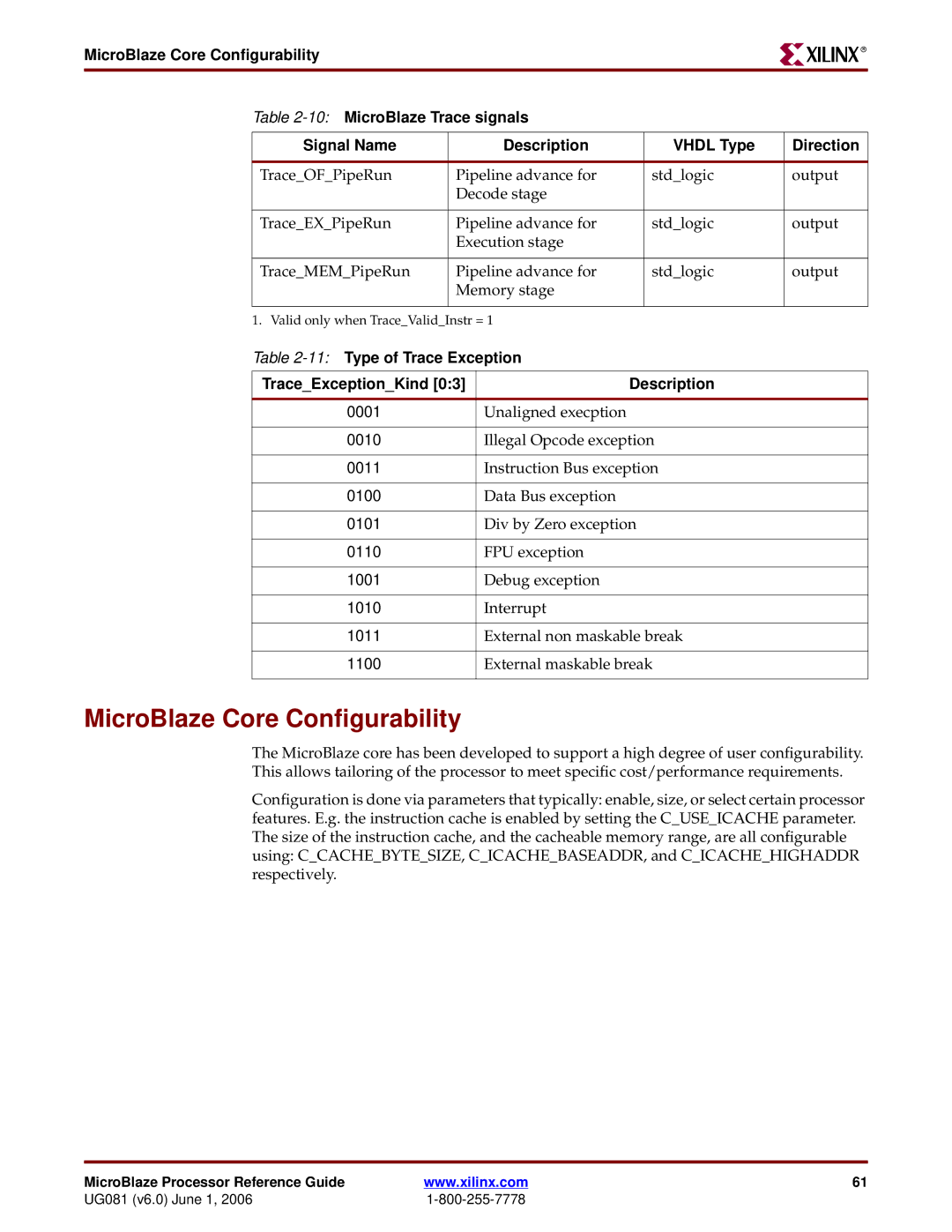

Signal Name |

| Description |

| VHDL Type | Direction |

|

|

|

|

|

|

Trace_OF_PipeRun | Pipeline advance for |

| std_logic | output | |

| Decode stage |

|

|

| |

|

|

|

|

|

|

Trace_EX_PipeRun | Pipeline advance for |

| std_logic | output | |

| Execution stage |

|

|

| |

|

|

|

|

|

|

Trace_MEM_PipeRun | Pipeline advance for |

| std_logic | output | |

| Memory stage |

|

|

| |

|

|

|

|

|

|

1. Valid only when Trace_Valid_Instr = 1 |

|

|

| ||

Table |

|

|

| ||

|

|

|

| ||

Trace_Exception_Kind [0:3] |

| Description |

| ||

|

|

|

|

|

|

0001 |

| Unaligned execption |

|

|

|

|

|

|

| ||

0010 |

| Illegal Opcode exception |

| ||

|

|

|

| ||

0011 |

| Instruction Bus exception |

| ||

|

|

|

|

|

|

0100 |

| Data Bus exception |

|

|

|

|

|

|

| ||

0101 |

| Div by Zero exception |

| ||

|

|

|

|

|

|

0110 |

| FPU exception |

|

|

|

|

|

|

|

|

|

1001 |

| Debug exception |

|

|

|

|

|

|

|

|

|

1010 |

| Interrupt |

|

|

|

|

|

|

| ||

1011 |

| External non maskable break |

| ||

|

|

|

| ||

1100 |

| External maskable break |

| ||

|

|

|

|

|

|

MicroBlaze Core Configurability

The MicroBlaze core has been developed to support a high degree of user configurability. This allows tailoring of the processor to meet specific cost/performance requirements.

Configuration is done via parameters that typically: enable, size, or select certain processor features. E.g. the instruction cache is enabled by setting the C_USE_ICACHE parameter. The size of the instruction cache, and the cacheable memory range, are all configurable using: C_CACHE_BYTE_SIZE, C_ICACHE_BASEADDR, and C_ICACHE_HIGHADDR respectively.

MicroBlaze Processor Reference Guide | www.xilinx.com | 61 |

UG081 (v6.0) June 1, 2006 |

|