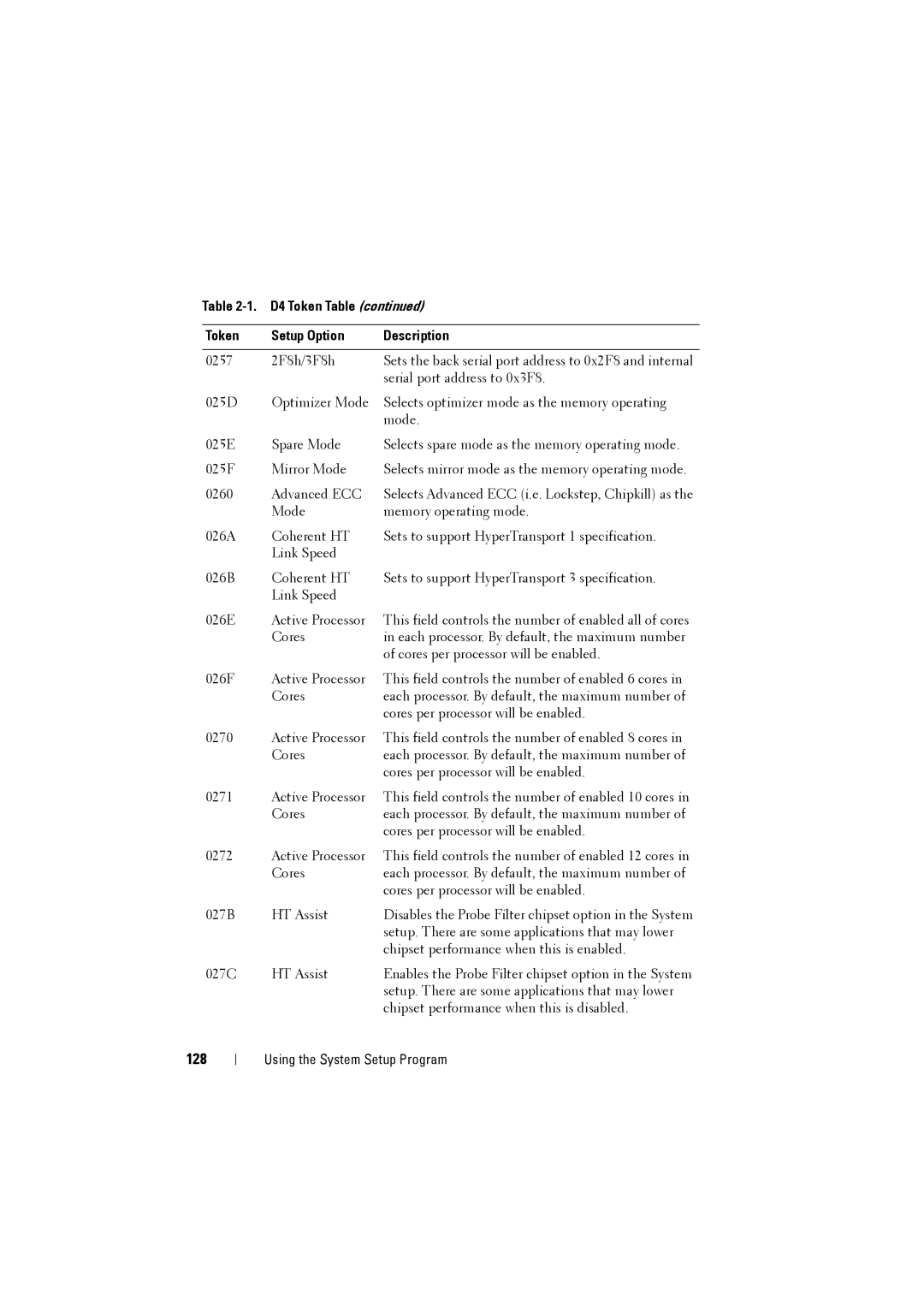

Table 2-1. D4 Token Table (continued)

Token | Setup Option | Description |

|

|

|

0257 | 2F8h/3F8h | Sets the back serial port address to 0x2F8 and internal |

|

| serial port address to 0x3F8. |

025D | Optimizer Mode | Selects optimizer mode as the memory operating |

|

| mode. |

025E | Spare Mode | Selects spare mode as the memory operating mode. |

025F | Mirror Mode | Selects mirror mode as the memory operating mode. |

0260 | Advanced ECC | Selects Advanced ECC (i.e. Lockstep, Chipkill) as the |

| Mode | memory operating mode. |

026A | Coherent HT | Sets to support HyperTransport 1 specification. |

| Link Speed |

|

026B | Coherent HT | Sets to support HyperTransport 3 specification. |

| Link Speed |

|

026E | Active Processor | This field controls the number of enabled all of cores |

| Cores | in each processor. By default, the maximum number |

|

| of cores per processor will be enabled. |

026F | Active Processor | This field controls the number of enabled 6 cores in |

| Cores | each processor. By default, the maximum number of |

|

| cores per processor will be enabled. |

0270 | Active Processor | This field controls the number of enabled 8 cores in |

| Cores | each processor. By default, the maximum number of |

|

| cores per processor will be enabled. |

0271 | Active Processor | This field controls the number of enabled 10 cores in |

| Cores | each processor. By default, the maximum number of |

|

| cores per processor will be enabled. |

0272 | Active Processor | This field controls the number of enabled 12 cores in |

| Cores | each processor. By default, the maximum number of |

|

| cores per processor will be enabled. |

027B | HT Assist | Disables the Probe Filter chipset option in the System |

|

| setup. There are some applications that may lower |

|

| chipset performance when this is enabled. |

027C | HT Assist | Enables the Probe Filter chipset option in the System |

|

| setup. There are some applications that may lower |

|

| chipset performance when this is disabled. |