www.ti.com

EMAC Port Registers

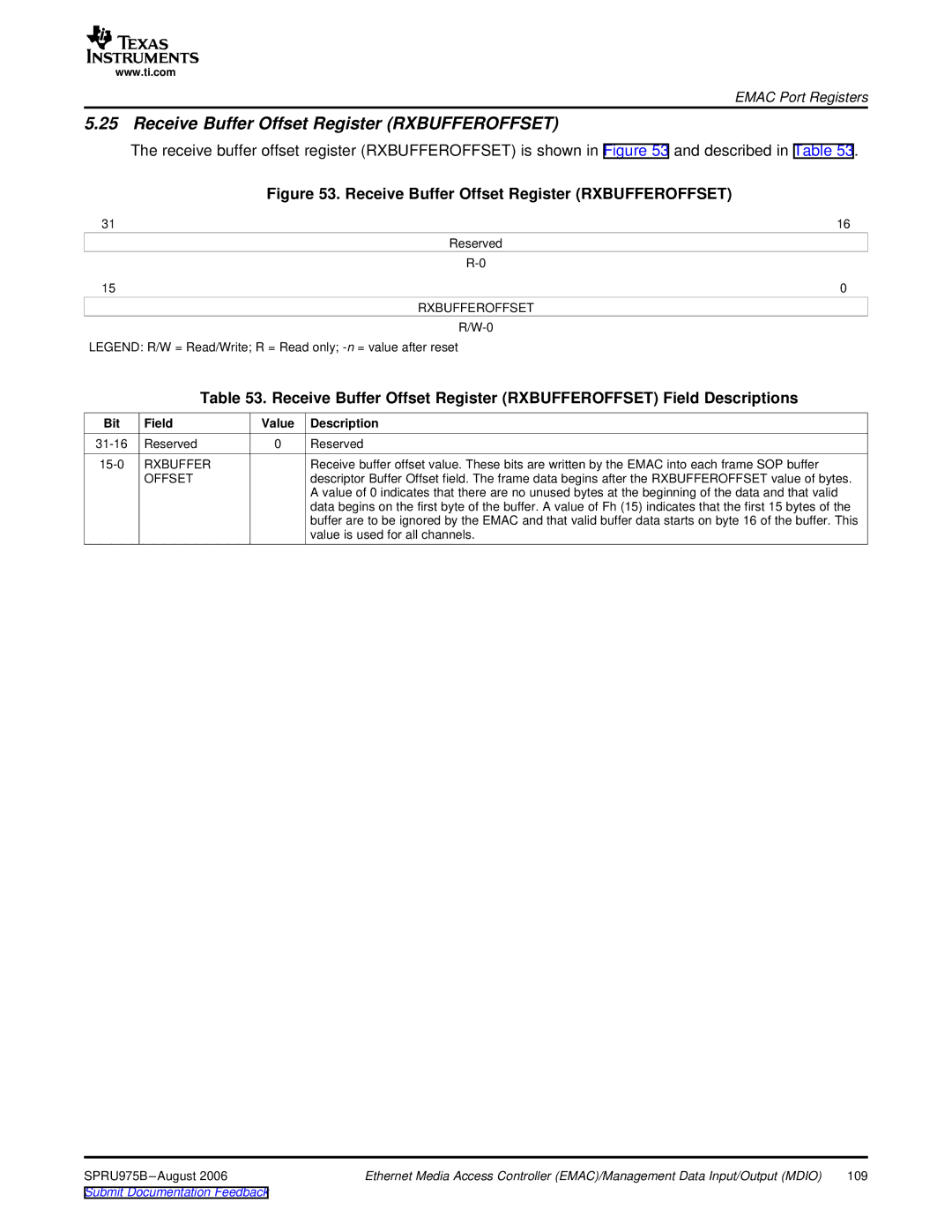

5.25 Receive Buffer Offset Register (RXBUFFEROFFSET)

The receive buffer offset register (RXBUFFEROFFSET) is shown in Figure 53 and described in Table 53.

| Figure 53. Receive Buffer Offset Register (RXBUFFEROFFSET) |

31 | 16 |

| Reserved |

| |

15 | 0 |

RXBUFFEROFFSET

LEGEND: R/W = Read/Write; R = Read only;

Table 53. Receive Buffer Offset Register (RXBUFFEROFFSET) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

RXBUFFER |

| Receive buffer offset value. These bits are written by the EMAC into each frame SOP buffer | |

| OFFSET |

| descriptor Buffer Offset field. The frame data begins after the RXBUFFEROFFSET value of bytes. |

|

|

| A value of 0 indicates that there are no unused bytes at the beginning of the data and that valid |

|

|

| data begins on the first byte of the buffer. A value of Fh (15) indicates that the first 15 bytes of the |

|

|

| buffer are to be ignored by the EMAC and that valid buffer data starts on byte 16 of the buffer. This |

|

|

| value is used for all channels. |

SPRU975B | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | 109 |