www.ti.com

EMAC Port Registers

5.27 Receive Channel

The receive channel

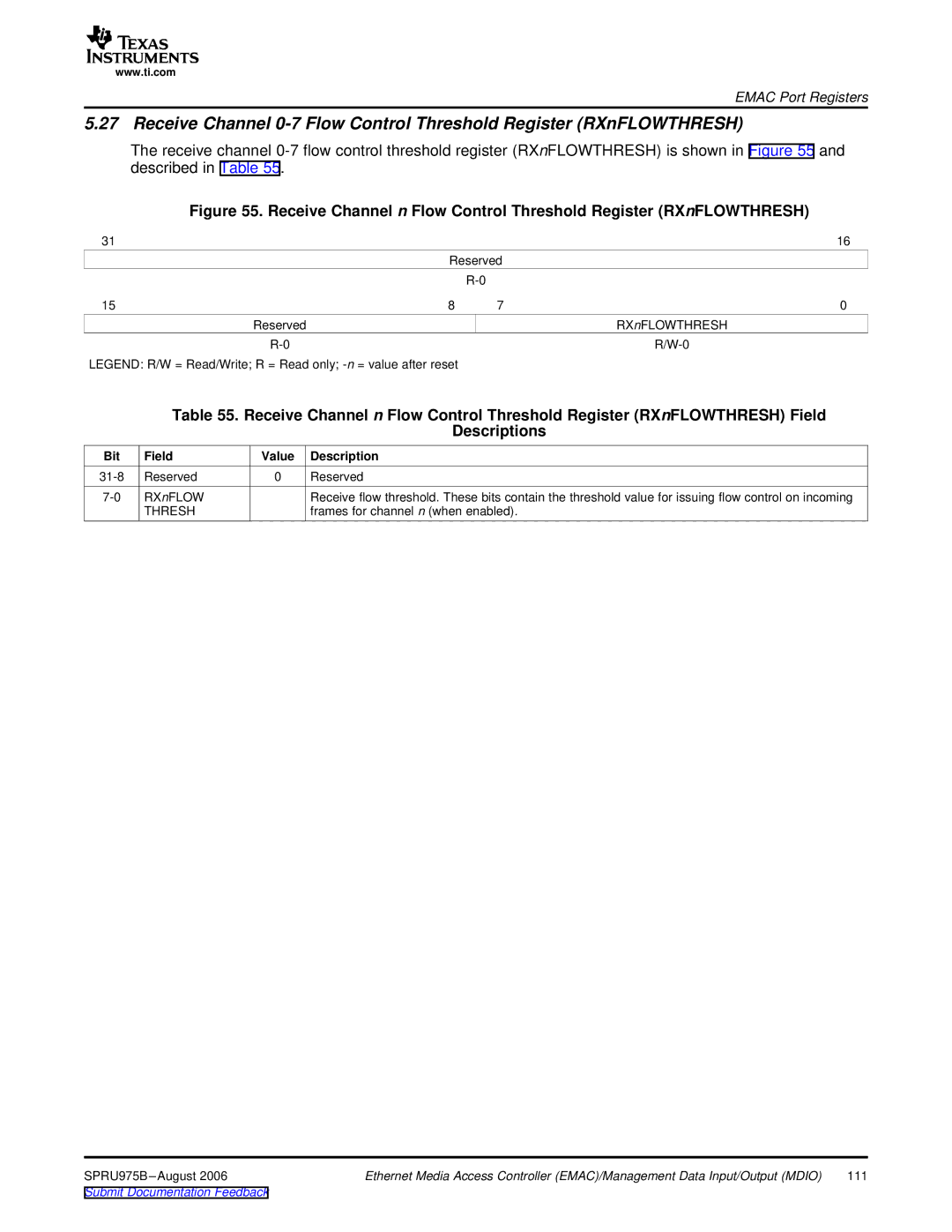

Figure 55. Receive Channel n Flow Control Threshold Register (RXnFLOWTHRESH)

31 |

|

| 16 |

| Reserved |

| |

|

|

| |

15 | 8 | 7 | 0 |

Reserved |

|

| RXnFLOWTHRESH |

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

Table 55. Receive Channel n Flow Control Threshold Register (RXnFLOWTHRESH) Field

Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

RXnFLOW |

| Receive flow threshold. These bits contain the threshold value for issuing flow control on incoming | |

| THRESH |

| frames for channel n (when enabled). |

SPRU975B | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | 111 |