www.ti.com

EMAC Port Registers

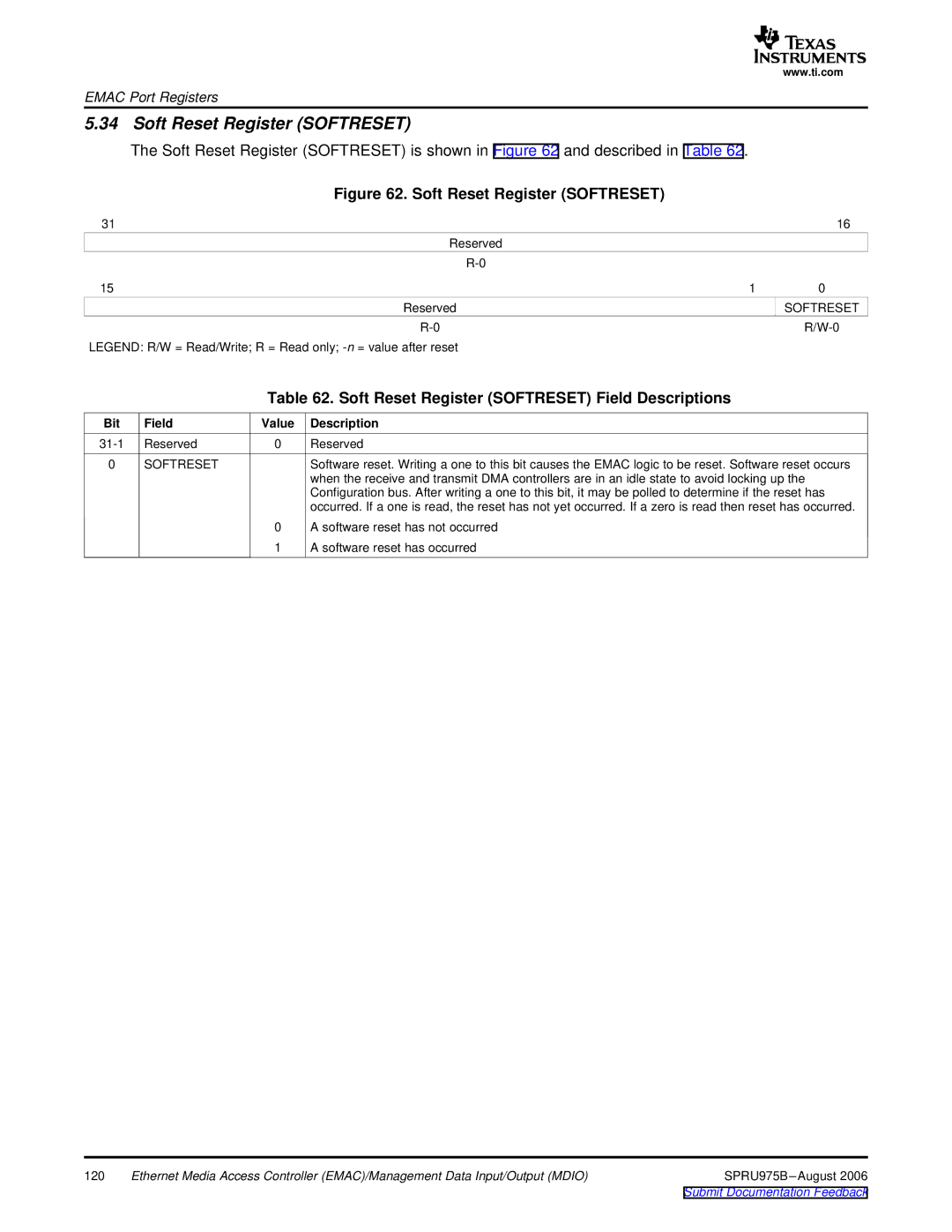

5.34 Soft Reset Register (SOFTRESET)

The Soft Reset Register (SOFTRESET) is shown in Figure 62 and described in Table 62.

Figure 62. Soft Reset Register (SOFTRESET)

31 |

| 16 |

Reserved |

|

|

|

| |

15 | 1 | 0 |

Reserved |

| SOFTRESET |

|

LEGEND: R/W = Read/Write; R = Read only;

Table 62. Soft Reset Register (SOFTRESET) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

0 | SOFTRESET |

| Software reset. Writing a one to this bit causes the EMAC logic to be reset. Software reset occurs |

|

|

| when the receive and transmit DMA controllers are in an idle state to avoid locking up the |

|

|

| Configuration bus. After writing a one to this bit, it may be polled to determine if the reset has |

|

|

| occurred. If a one is read, the reset has not yet occurred. If a zero is read then reset has occurred. |

|

| 0 | A software reset has not occurred |

|

| 1 | A software reset has occurred |

120 | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | SPRU975B |