|

| 4.15 | MDIO User PHY Select Register 1 (USERPHYSEL1) | 80 |

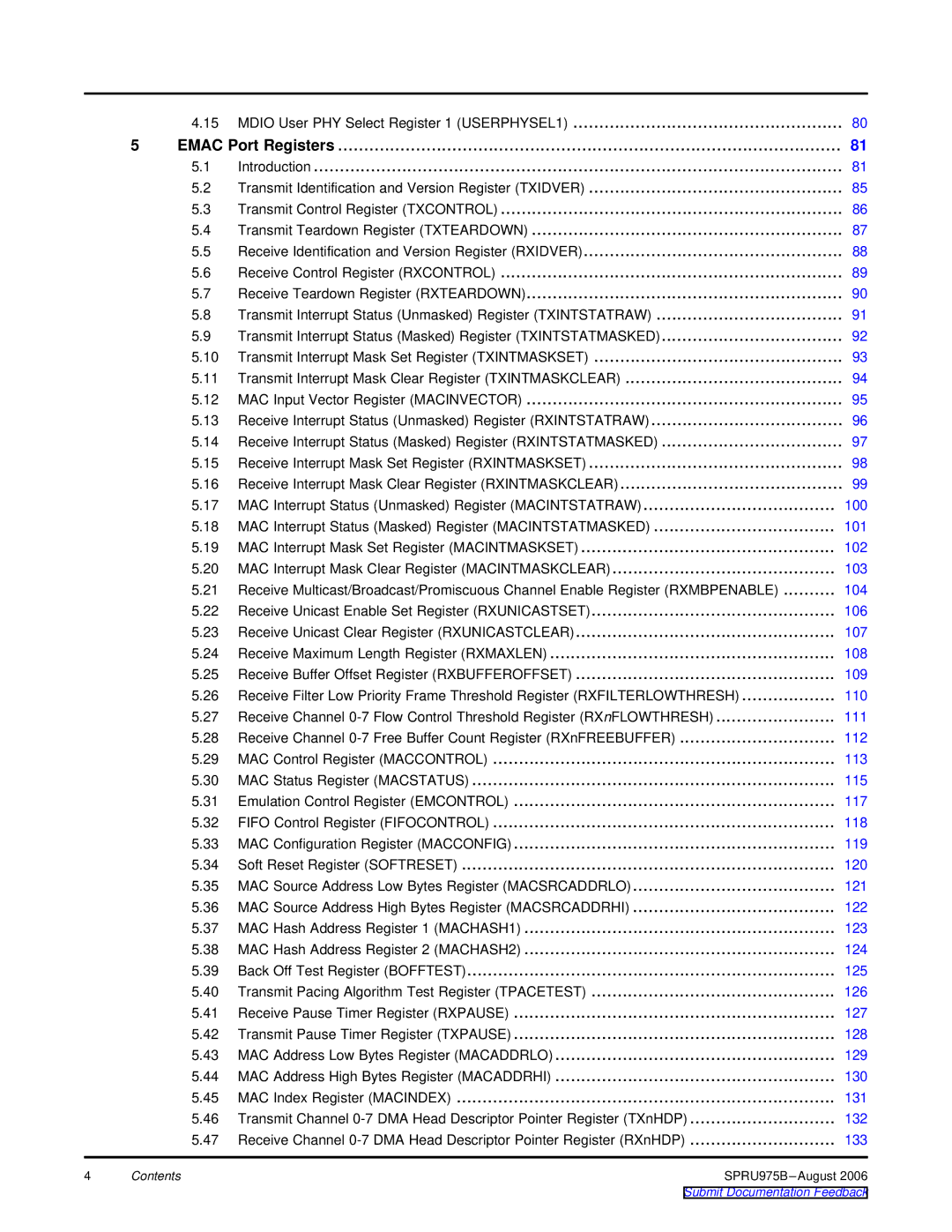

| 5 | EMAC Port Registers | 81 | |

|

| 5.1 | Introduction | 81 |

|

| 5.2 | Transmit Identification and Version Register (TXIDVER) | 85 |

|

| 5.3 | Transmit Control Register (TXCONTROL) | 86 |

|

| 5.4 | Transmit Teardown Register (TXTEARDOWN) | 87 |

|

| 5.5 | Receive Identification and Version Register (RXIDVER) | 88 |

|

| 5.6 | Receive Control Register (RXCONTROL) | 89 |

|

| 5.7 | Receive Teardown Register (RXTEARDOWN) | 90 |

|

| 5.8 | Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW) | 91 |

|

| 5.9 | Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) | 92 |

|

| 5.10 | Transmit Interrupt Mask Set Register (TXINTMASKSET) | 93 |

|

| 5.11 | Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR) | 94 |

|

| 5.12 | MAC Input Vector Register (MACINVECTOR) | 95 |

|

| 5.13 | Receive Interrupt Status (Unmasked) Register (RXINTSTATRAW) | 96 |

|

| 5.14 | Receive Interrupt Status (Masked) Register (RXINTSTATMASKED) | 97 |

|

| 5.15 | Receive Interrupt Mask Set Register (RXINTMASKSET) | 98 |

|

| 5.16 | Receive Interrupt Mask Clear Register (RXINTMASKCLEAR) | 99 |

|

| 5.17 | MAC Interrupt Status (Unmasked) Register (MACINTSTATRAW) | 100 |

|

| 5.18 | MAC Interrupt Status (Masked) Register (MACINTSTATMASKED) | 101 |

|

| 5.19 | MAC Interrupt Mask Set Register (MACINTMASKSET) | 102 |

|

| 5.20 | MAC Interrupt Mask Clear Register (MACINTMASKCLEAR) | 103 |

|

| 5.21 | Receive Multicast/Broadcast/Promiscuous Channel Enable Register (RXMBPENABLE) | 104 |

|

| 5.22 | Receive Unicast Enable Set Register (RXUNICASTSET) | 106 |

|

| 5.23 | Receive Unicast Clear Register (RXUNICASTCLEAR) | 107 |

|

| 5.24 | Receive Maximum Length Register (RXMAXLEN) | 108 |

|

| 5.25 | Receive Buffer Offset Register (RXBUFFEROFFSET) | 109 |

|

| 5.26 | Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH) | 110 |

|

| 5.27 | Receive Channel | 111 |

|

| 5.28 | Receive Channel | 112 |

|

| 5.29 | MAC Control Register (MACCONTROL) | 113 |

|

| 5.30 | MAC Status Register (MACSTATUS) | 115 |

|

| 5.31 | Emulation Control Register (EMCONTROL) | 117 |

|

| 5.32 | FIFO Control Register (FIFOCONTROL) | 118 |

|

| 5.33 | MAC Configuration Register (MACCONFIG) | 119 |

|

| 5.34 | Soft Reset Register (SOFTRESET) | 120 |

|

| 5.35 | MAC Source Address Low Bytes Register (MACSRCADDRLO) | 121 |

|

| 5.36 | MAC Source Address High Bytes Register (MACSRCADDRHI) | 122 |

|

| 5.37 | MAC Hash Address Register 1 (MACHASH1) | 123 |

|

| 5.38 | MAC Hash Address Register 2 (MACHASH2) | 124 |

|

| 5.39 | Back Off Test Register (BOFFTEST) | 125 |

|

| 5.40 | Transmit Pacing Algorithm Test Register (TPACETEST) | 126 |

|

| 5.41 | Receive Pause Timer Register (RXPAUSE) | 127 |

|

| 5.42 | Transmit Pause Timer Register (TXPAUSE) | 128 |

|

| 5.43 | MAC Address Low Bytes Register (MACADDRLO) | 129 |

|

| 5.44 | MAC Address High Bytes Register (MACADDRHI) | 130 |

|

| 5.45 | MAC Index Register (MACINDEX) | 131 |

|

| 5.46 | Transmit Channel | 132 |

|

| 5.47 | Receive Channel | 133 |

4 | Contents | SPRU975B | ||