www.ti.com

EMAC Functional Architecture

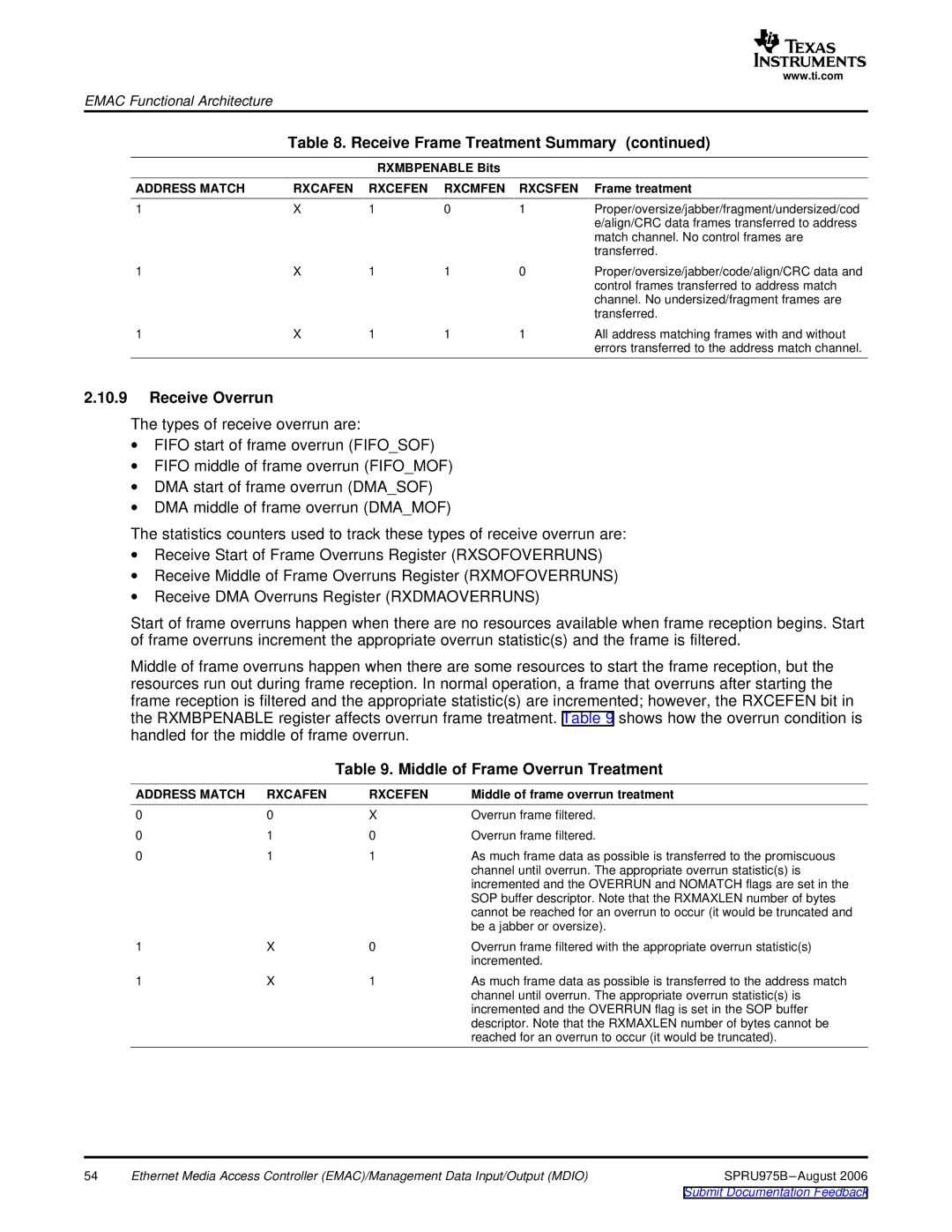

Table 8. Receive Frame Treatment Summary (continued)

|

| RXMBPENABLE Bits |

|

| |

ADDRESS MATCH | RXCAFEN | RXCEFEN | RXCMFEN | RXCSFEN | Frame treatment |

1 | X | 1 | 0 | 1 | Proper/oversize/jabber/fragment/undersized/cod |

|

|

|

|

| e/align/CRC data frames transferred to address |

|

|

|

|

| match channel. No control frames are |

|

|

|

|

| transferred. |

1 | X | 1 | 1 | 0 | Proper/oversize/jabber/code/align/CRC data and |

|

|

|

|

| control frames transferred to address match |

|

|

|

|

| channel. No undersized/fragment frames are |

|

|

|

|

| transferred. |

1 | X | 1 | 1 | 1 | All address matching frames with and without |

|

|

|

|

| errors transferred to the address match channel. |

2.10.9Receive Overrun

The types of receive overrun are:

∙FIFO start of frame overrun (FIFO_SOF)

∙FIFO middle of frame overrun (FIFO_MOF)

∙DMA start of frame overrun (DMA_SOF)

∙DMA middle of frame overrun (DMA_MOF)

The statistics counters used to track these types of receive overrun are:

∙Receive Start of Frame Overruns Register (RXSOFOVERRUNS)

∙Receive Middle of Frame Overruns Register (RXMOFOVERRUNS)

∙Receive DMA Overruns Register (RXDMAOVERRUNS)

Start of frame overruns happen when there are no resources available when frame reception begins. Start of frame overruns increment the appropriate overrun statistic(s) and the frame is filtered.

Middle of frame overruns happen when there are some resources to start the frame reception, but the resources run out during frame reception. In normal operation, a frame that overruns after starting the frame reception is filtered and the appropriate statistic(s) are incremented; however, the RXCEFEN bit in the RXMBPENABLE register affects overrun frame treatment. Table 9 shows how the overrun condition is handled for the middle of frame overrun.

Table 9. Middle of Frame Overrun Treatment

ADDRESS MATCH | RXCAFEN | RXCEFEN | Middle of frame overrun treatment |

0 | 0 | X | Overrun frame filtered. |

0 | 1 | 0 | Overrun frame filtered. |

0 | 1 | 1 | As much frame data as possible is transferred to the promiscuous |

|

|

| channel until overrun. The appropriate overrun statistic(s) is |

|

|

| incremented and the OVERRUN and NOMATCH flags are set in the |

|

|

| SOP buffer descriptor. Note that the RXMAXLEN number of bytes |

|

|

| cannot be reached for an overrun to occur (it would be truncated and |

|

|

| be a jabber or oversize). |

1 | X | 0 | Overrun frame filtered with the appropriate overrun statistic(s) |

|

|

| incremented. |

1 | X | 1 | As much frame data as possible is transferred to the address match |

|

|

| channel until overrun. The appropriate overrun statistic(s) is |

|

|

| incremented and the OVERRUN flag is set in the SOP buffer |

|

|

| descriptor. Note that the RXMAXLEN number of bytes cannot be |

|

|

| reached for an overrun to occur (it would be truncated). |

54 | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | SPRU975B |