www.ti.com

EMAC Functional Architecture

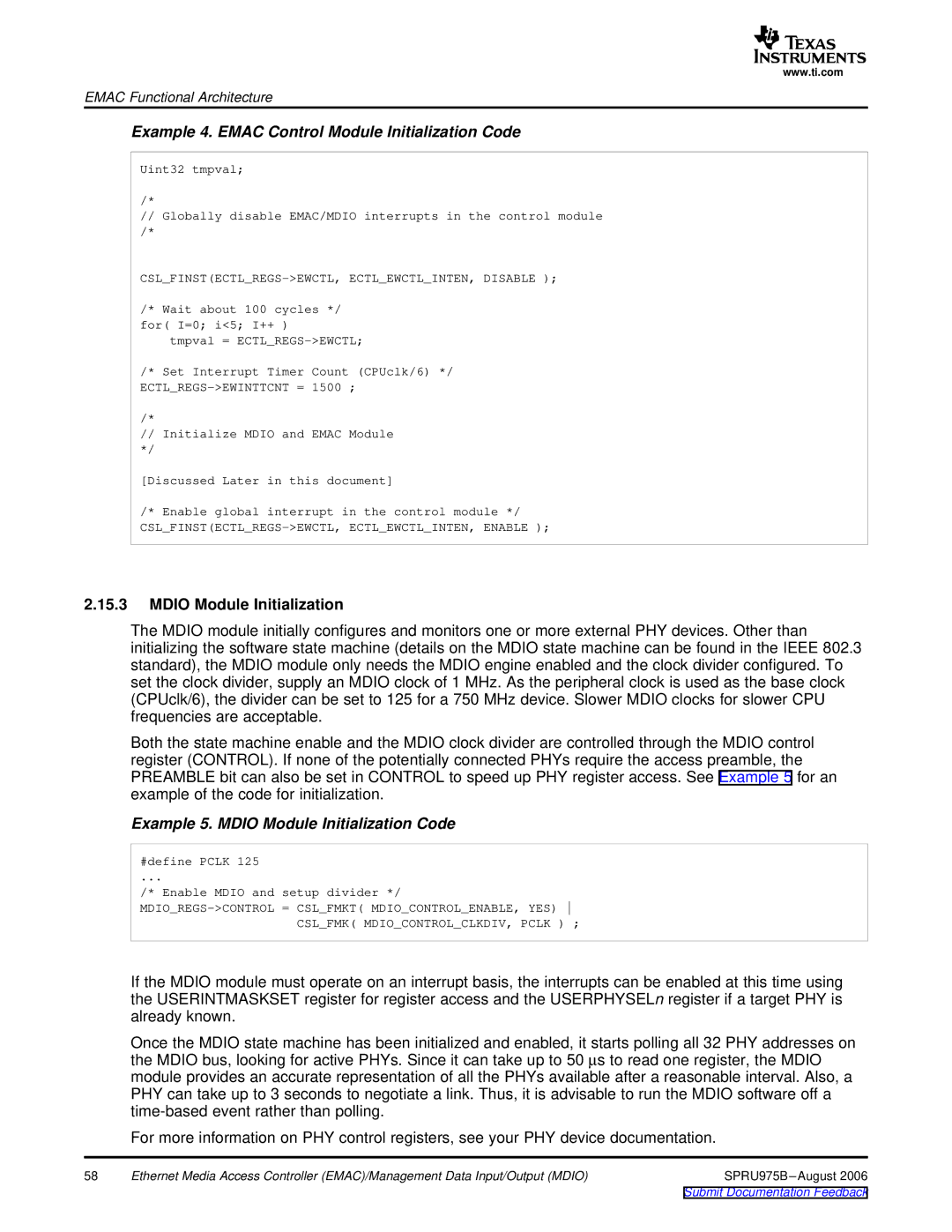

Example 4. EMAC Control Module Initialization Code

Uint32 tmpval;

/*

//Globally disable EMAC/MDIO interrupts in the control module

/*

CSL_FINST(ECTL_REGS->EWCTL, ECTL_EWCTL_INTEN, DISABLE );

/* Wait about 100 cycles */ for( I=0; i<5; I++ )

tmpval =

/* Set Interrupt Timer Count (CPUclk/6) */

/*

//Initialize MDIO and EMAC Module

*/

[Discussed Later in this document]

/* Enable global interrupt in the control module */

2.15.3MDIO Module Initialization

The MDIO module initially configures and monitors one or more external PHY devices. Other than initializing the software state machine (details on the MDIO state machine can be found in the IEEE 802.3 standard), the MDIO module only needs the MDIO engine enabled and the clock divider configured. To set the clock divider, supply an MDIO clock of 1 MHz. As the peripheral clock is used as the base clock (CPUclk/6), the divider can be set to 125 for a 750 MHz device. Slower MDIO clocks for slower CPU frequencies are acceptable.

Both the state machine enable and the MDIO clock divider are controlled through the MDIO control register (CONTROL). If none of the potentially connected PHYs require the access preamble, the PREAMBLE bit can also be set in CONTROL to speed up PHY register access. See Example 5 for an example of the code for initialization.

Example 5. MDIO Module Initialization Code

#define PCLK 125

...

/* Enable MDIO and setup divider */

If the MDIO module must operate on an interrupt basis, the interrupts can be enabled at this time using the USERINTMASKSET register for register access and the USERPHYSELn register if a target PHY is already known.

Once the MDIO state machine has been initialized and enabled, it starts polling all 32 PHY addresses on the MDIO bus, looking for active PHYs. Since it can take up to 50 μs to read one register, the MDIO module provides an accurate representation of all the PHYs available after a reasonable interval. Also, a PHY can take up to 3 seconds to negotiate a link. Thus, it is advisable to run the MDIO software off a

For more information on PHY control registers, see your PHY device documentation.

58 | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | SPRU975B |