www.ti.com

EMAC Port Registers

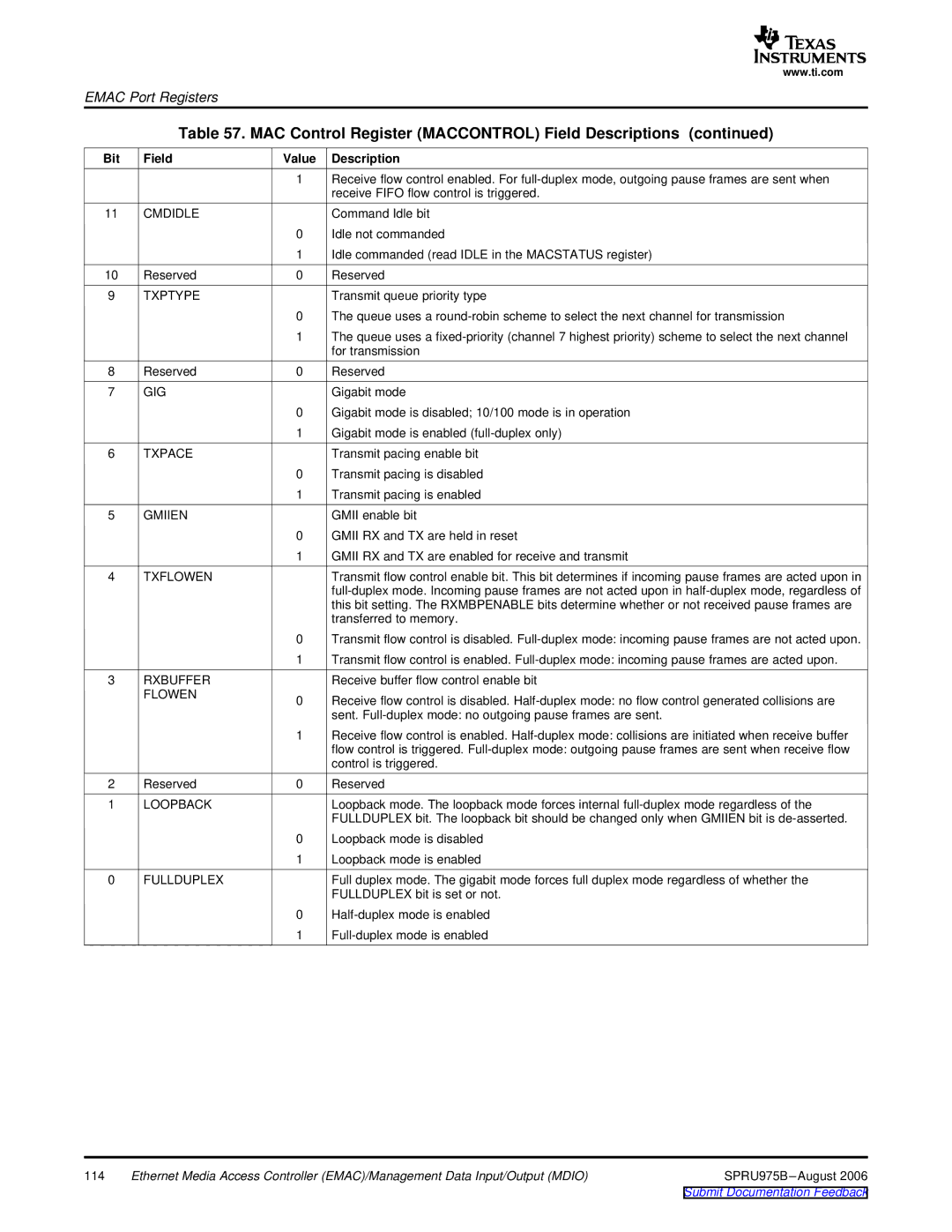

Table 57. MAC Control Register (MACCONTROL) Field Descriptions (continued)

Bit | Field | Value | Description |

|

| 1 | Receive flow control enabled. For |

|

|

| receive FIFO flow control is triggered. |

11 | CMDIDLE |

| Command Idle bit |

|

| 0 | Idle not commanded |

|

| 1 | Idle commanded (read IDLE in the MACSTATUS register) |

10 | Reserved | 0 | Reserved |

9 | TXPTYPE |

| Transmit queue priority type |

|

| 0 | The queue uses a |

|

| 1 | The queue uses a |

|

|

| for transmission |

8 | Reserved | 0 | Reserved |

7 | GIG |

| Gigabit mode |

|

| 0 | Gigabit mode is disabled; 10/100 mode is in operation |

|

| 1 | Gigabit mode is enabled |

6 | TXPACE |

| Transmit pacing enable bit |

|

| 0 | Transmit pacing is disabled |

|

| 1 | Transmit pacing is enabled |

5 | GMIIEN |

| GMII enable bit |

|

| 0 | GMII RX and TX are held in reset |

|

| 1 | GMII RX and TX are enabled for receive and transmit |

4 | TXFLOWEN |

| Transmit flow control enable bit. This bit determines if incoming pause frames are acted upon in |

|

|

| |

|

|

| this bit setting. The RXMBPENABLE bits determine whether or not received pause frames are |

|

|

| transferred to memory. |

|

| 0 | Transmit flow control is disabled. |

|

| 1 | Transmit flow control is enabled. |

3 | RXBUFFER |

| Receive buffer flow control enable bit |

| FLOWEN | 0 | Receive flow control is disabled. |

|

| ||

|

|

| sent. |

|

| 1 | Receive flow control is enabled. |

|

|

| flow control is triggered. |

|

|

| control is triggered. |

2 | Reserved | 0 | Reserved |

1 | LOOPBACK |

| Loopback mode. The loopback mode forces internal |

|

|

| FULLDUPLEX bit. The loopback bit should be changed only when GMIIEN bit is |

|

| 0 | Loopback mode is disabled |

|

| 1 | Loopback mode is enabled |

0 | FULLDUPLEX |

| Full duplex mode. The gigabit mode forces full duplex mode regardless of whether the |

|

|

| FULLDUPLEX bit is set or not. |

|

| 0 | |

|

| 1 |

114 | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | SPRU975B |