www.ti.com

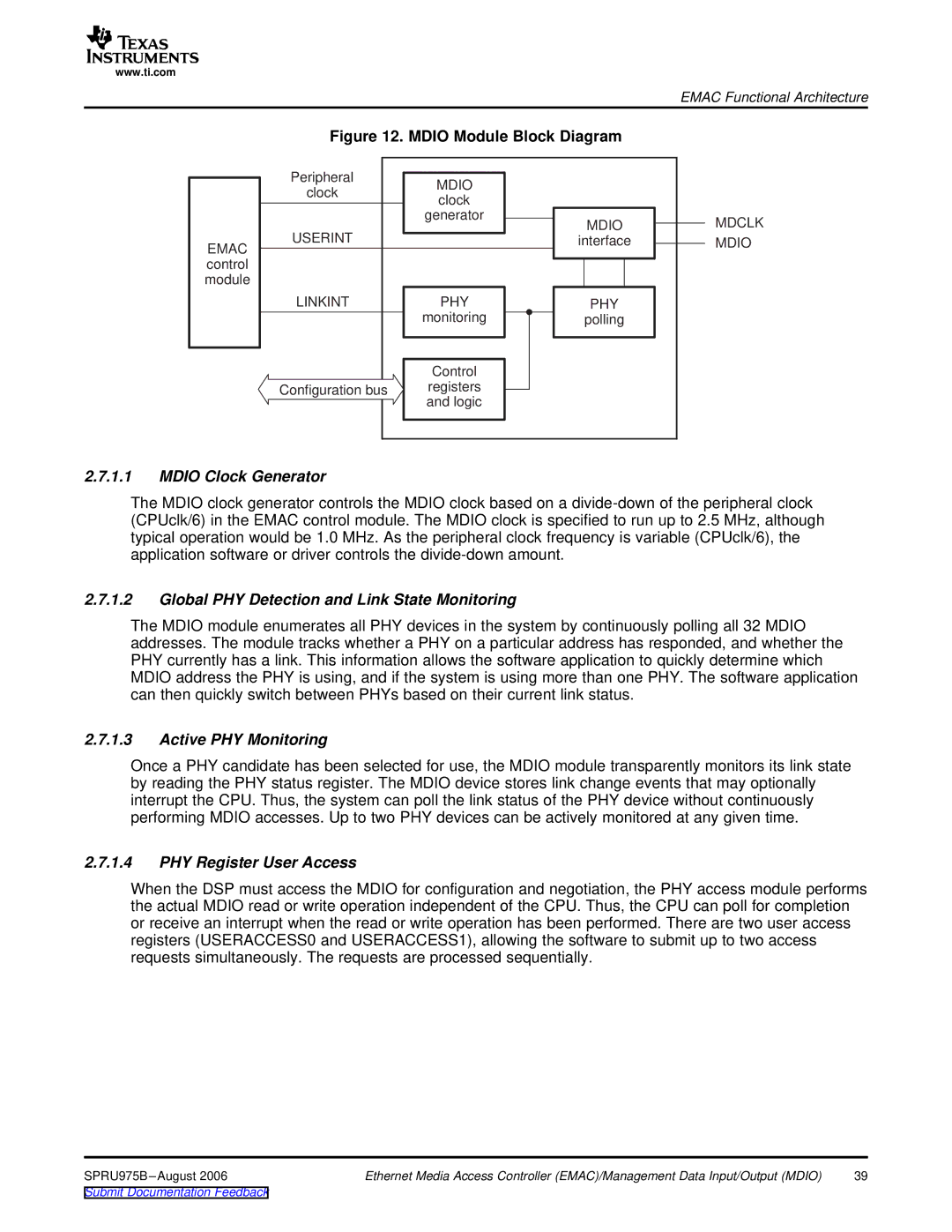

Figure 12. MDIO Module Block Diagram | ||

Peripheral | MDIO |

|

clock |

| |

clock |

| |

|

| |

| generator | MDIO |

USERINT |

| |

| interface | |

EMAC |

|

|

control |

|

|

module |

|

|

LINKINT | PHY | PHY |

| monitoring | polling |

| Control |

|

Configuration bus | registers |

|

| and logic |

|

EMAC Functional Architecture

MDCLK

MDIO

2.7.1.1MDIO Clock Generator

The MDIO clock generator controls the MDIO clock based on a

2.7.1.2Global PHY Detection and Link State Monitoring

The MDIO module enumerates all PHY devices in the system by continuously polling all 32 MDIO addresses. The module tracks whether a PHY on a particular address has responded, and whether the PHY currently has a link. This information allows the software application to quickly determine which MDIO address the PHY is using, and if the system is using more than one PHY. The software application can then quickly switch between PHYs based on their current link status.

2.7.1.3Active PHY Monitoring

Once a PHY candidate has been selected for use, the MDIO module transparently monitors its link state by reading the PHY status register. The MDIO device stores link change events that may optionally interrupt the CPU. Thus, the system can poll the link status of the PHY device without continuously performing MDIO accesses. Up to two PHY devices can be actively monitored at any given time.

2.7.1.4PHY Register User Access

When the DSP must access the MDIO for configuration and negotiation, the PHY access module performs the actual MDIO read or write operation independent of the CPU. Thus, the CPU can poll for completion or receive an interrupt when the read or write operation has been performed. There are two user access registers (USERACCESS0 and USERACCESS1), allowing the software to submit up to two access requests simultaneously. The requests are processed sequentially.

SPRU975B | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | 39 |