www.ti.com

EMAC Functional Architecture

2.3System Level Connections

The C645x device supports four different interfaces to a physical layer device. You can only transfer data on one interface at a given time. Each of these interfaces is selected in hardware via the configuration pins (MACSEL[1:0]).

Table 1 shows the possible settings for these configuration pins.

Table 1. Interface Selection Pins

MACSEL [1:0] | Interface |

00 | MII |

01 | RMII |

10 | GMII |

11 | RGMII |

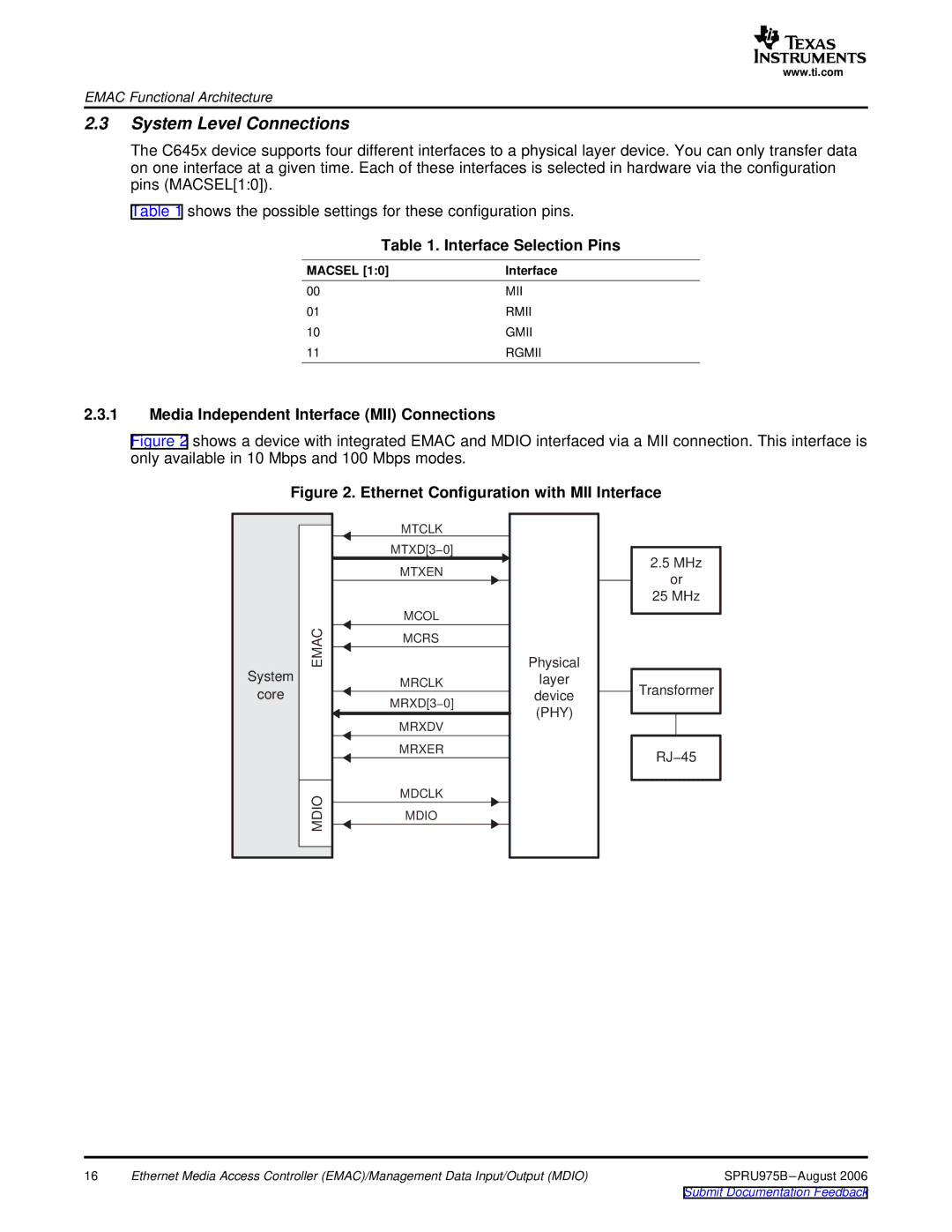

2.3.1Media Independent Interface (MII) Connections

Figure 2 shows a device with integrated EMAC and MDIO interfaced via a MII connection. This interface is only available in 10 Mbps and 100 Mbps modes.

Figure 2. Ethernet Configuration with MII Interface

System

core

EMAC

MDIO

MTCLK

MTXD[3−0]

MTXEN

MCOL

MCRS

MRCLK

MRXD[3−0]

MRXDV

MRXER

MDCLK

MDIO

Physical layer device (PHY)

2.5 MHz

or

25 MHz

Transformer

RJ−45

16 | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | SPRU975B |