www.ti.com

EMAC Functional Architecture

2.3.4Reduced Gigabit Media Independent Interface (RGMII) Connections

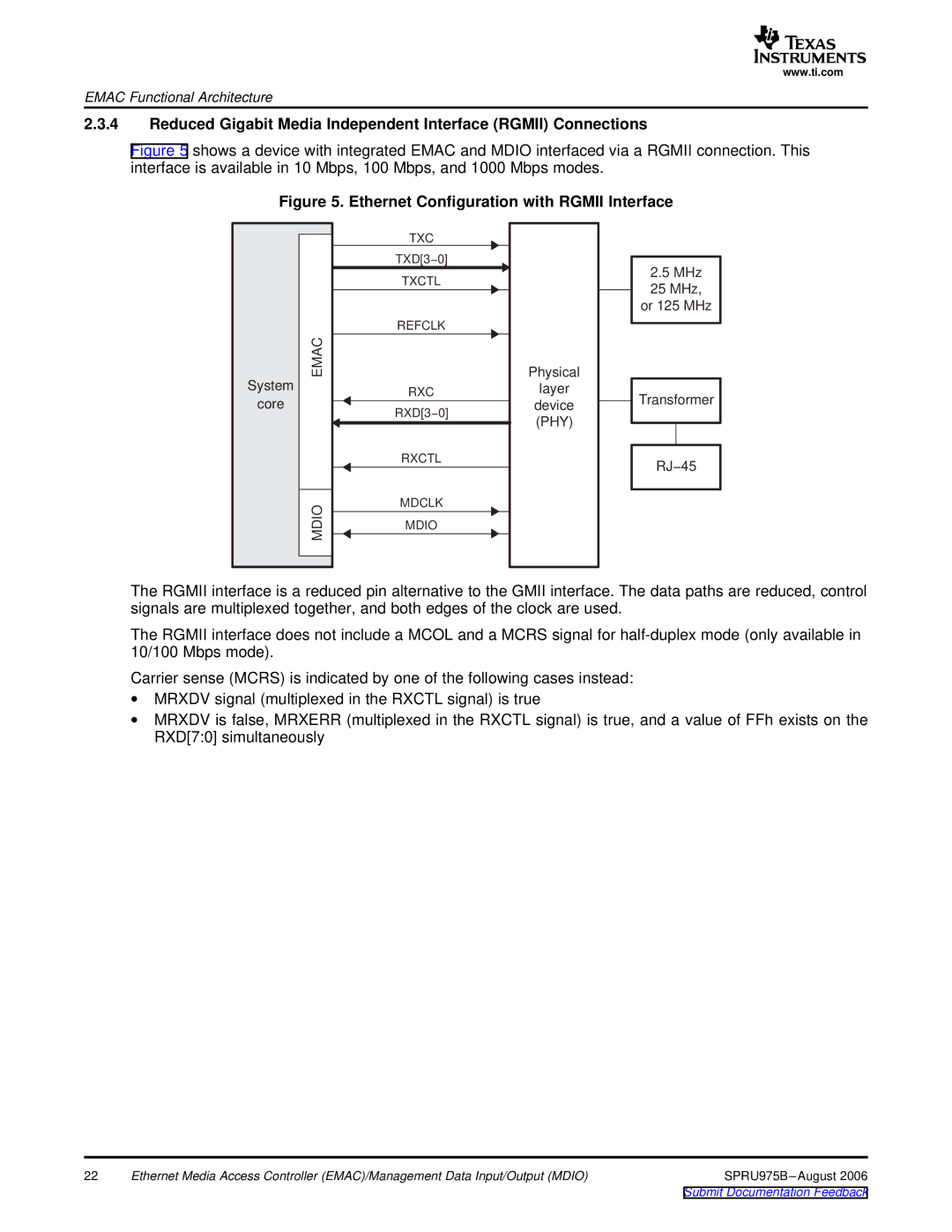

Figure 5 shows a device with integrated EMAC and MDIO interfaced via a RGMII connection. This interface is available in 10 Mbps, 100 Mbps, and 1000 Mbps modes.

Figure 5. Ethernet Configuration with RGMII Interface

System

core

EMAC

MDIO

TXC

TXD[3−0]

TXCTL

REFCLK

RXC

RXD[3−0]

RXCTL

MDCLK

MDIO

Physical layer device (PHY)

2.5MHz 25 MHz,

or 125 MHz

Transformer

RJ−45

The RGMII interface is a reduced pin alternative to the GMII interface. The data paths are reduced, control signals are multiplexed together, and both edges of the clock are used.

The RGMII interface does not include a MCOL and a MCRS signal for

Carrier sense (MCRS) is indicated by one of the following cases instead:

∙MRXDV signal (multiplexed in the RXCTL signal) is true

∙MRXDV is false, MRXERR (multiplexed in the RXCTL signal) is true, and a value of FFh exists on the RXD[7:0] simultaneously

22 | Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) | SPRU975B |