Intel® NetStructureTMZT 7102 Chassis Management Module

Hardware Specifications

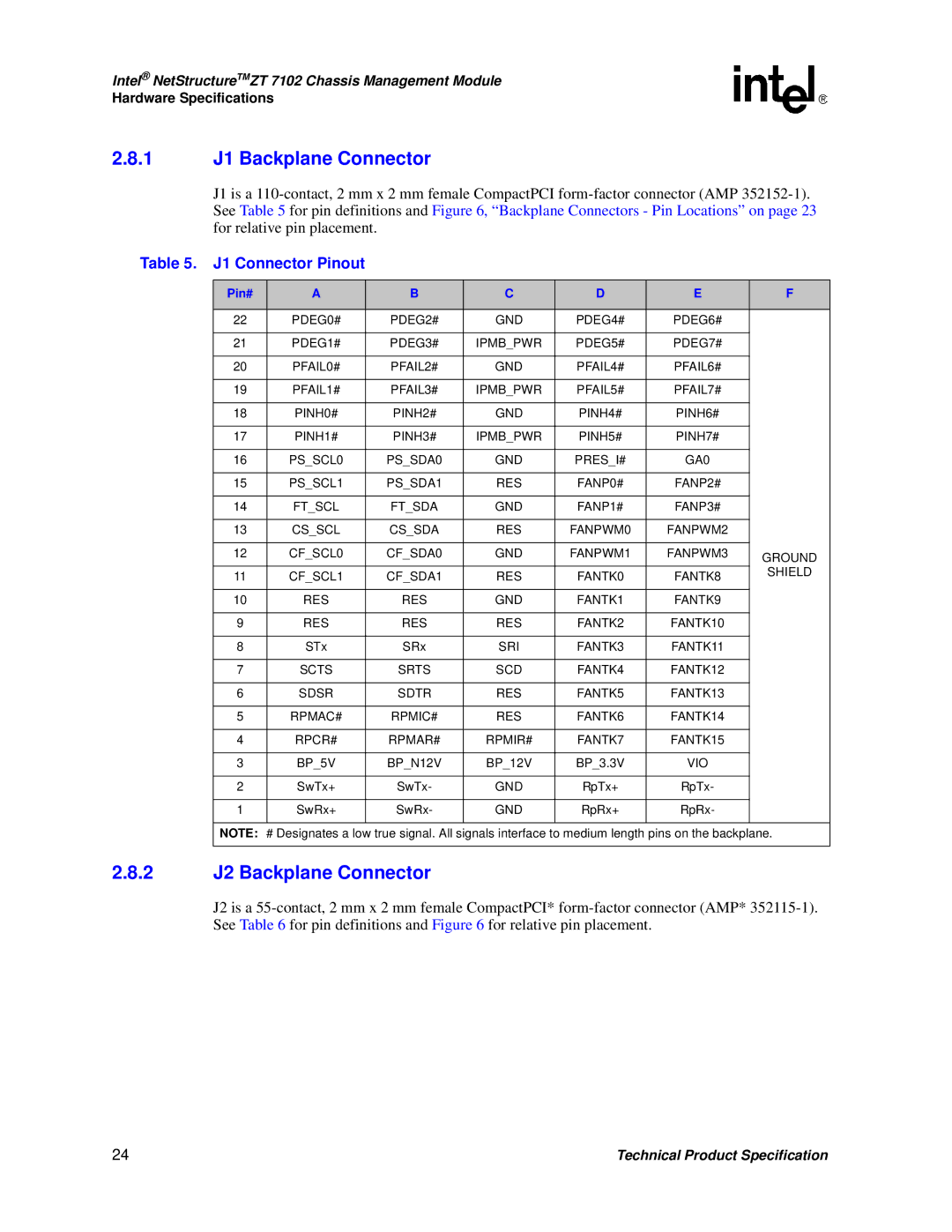

2.8.1J1 Backplane Connector

J1 is a

Table 5. J1 Connector Pinout

Pin# | A | B | C | D | E | F |

|

|

|

|

|

|

|

22 | PDEG0# | PDEG2# | GND | PDEG4# | PDEG6# |

|

|

|

|

|

|

|

|

21 | PDEG1# | PDEG3# | IPMB_PWR | PDEG5# | PDEG7# |

|

|

|

|

|

|

|

|

20 | PFAIL0# | PFAIL2# | GND | PFAIL4# | PFAIL6# |

|

|

|

|

|

|

|

|

19 | PFAIL1# | PFAIL3# | IPMB_PWR | PFAIL5# | PFAIL7# |

|

|

|

|

|

|

|

|

18 | PINH0# | PINH2# | GND | PINH4# | PINH6# |

|

|

|

|

|

|

|

|

17 | PINH1# | PINH3# | IPMB_PWR | PINH5# | PINH7# |

|

|

|

|

|

|

|

|

16 | PS_SCL0 | PS_SDA0 | GND | PRES_I# | GA0 |

|

|

|

|

|

|

|

|

15 | PS_SCL1 | PS_SDA1 | RES | FANP0# | FANP2# |

|

|

|

|

|

|

|

|

14 | FT_SCL | FT_SDA | GND | FANP1# | FANP3# |

|

|

|

|

|

|

|

|

13 | CS_SCL | CS_SDA | RES | FANPWM0 | FANPWM2 |

|

|

|

|

|

|

|

|

12 | CF_SCL0 | CF_SDA0 | GND | FANPWM1 | FANPWM3 | GROUND |

|

|

|

|

|

| |

11 | CF_SCL1 | CF_SDA1 | RES | FANTK0 | FANTK8 | SHIELD |

| ||||||

|

|

|

|

|

|

|

10 | RES | RES | GND | FANTK1 | FANTK9 |

|

|

|

|

|

|

|

|

9 | RES | RES | RES | FANTK2 | FANTK10 |

|

|

|

|

|

|

|

|

8 | STx | SRx | SRI | FANTK3 | FANTK11 |

|

|

|

|

|

|

|

|

7 | SCTS | SRTS | SCD | FANTK4 | FANTK12 |

|

|

|

|

|

|

|

|

6 | SDSR | SDTR | RES | FANTK5 | FANTK13 |

|

|

|

|

|

|

|

|

5 | RPMAC# | RPMIC# | RES | FANTK6 | FANTK14 |

|

|

|

|

|

|

|

|

4 | RPCR# | RPMAR# | RPMIR# | FANTK7 | FANTK15 |

|

|

|

|

|

|

|

|

3 | BP_5V | BP_N12V | BP_12V | BP_3.3V | VIO |

|

|

|

|

|

|

|

|

2 | SwTx+ | SwTx- | GND | RpTx+ | RpTx- |

|

|

|

|

|

|

|

|

1 | SwRx+ | SwRx- | GND | RpRx+ | RpRx- |

|

|

|

|

|

|

|

|

NOTE: # Designates a low true signal. All signals interface to medium length pins on the backplane.

2.8.2J2 Backplane Connector

J2 is a

24 | Technical Product Specification |