Intel® NetStructureTMZT 7102 Chassis Management Module

Hardware Specifications

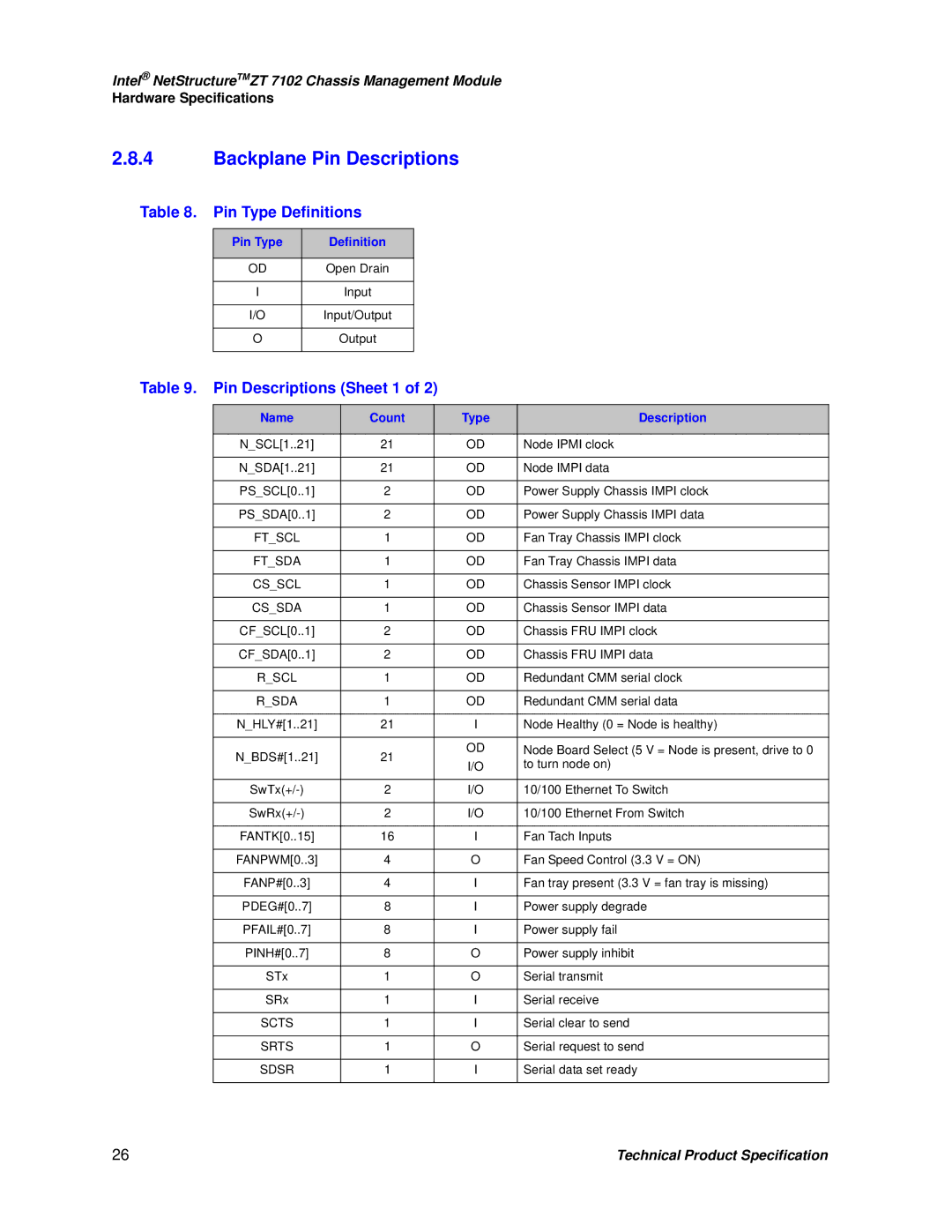

2.8.4Backplane Pin Descriptions

Table 8. Pin Type Definitions

Pin Type | Definition |

|

|

OD | Open Drain |

|

|

I | Input |

|

|

I/O | Input/Output |

|

|

O | Output |

|

|

Table 9. Pin Descriptions (Sheet 1 of 2)

Name | Count | Type | Description | |

|

|

|

| |

N_SCL[1..21] | 21 | OD | Node IPMI clock | |

|

|

|

| |

N_SDA[1..21] | 21 | OD | Node IMPI data | |

|

|

|

| |

PS_SCL[0..1] | 2 | OD | Power Supply Chassis IMPI clock | |

|

|

|

| |

PS_SDA[0..1] | 2 | OD | Power Supply Chassis IMPI data | |

|

|

|

| |

FT_SCL | 1 | OD | Fan Tray Chassis IMPI clock | |

|

|

|

| |

FT_SDA | 1 | OD | Fan Tray Chassis IMPI data | |

|

|

|

| |

CS_SCL | 1 | OD | Chassis Sensor IMPI clock | |

|

|

|

| |

CS_SDA | 1 | OD | Chassis Sensor IMPI data | |

|

|

|

| |

CF_SCL[0..1] | 2 | OD | Chassis FRU IMPI clock | |

|

|

|

| |

CF_SDA[0..1] | 2 | OD | Chassis FRU IMPI data | |

|

|

|

| |

R_SCL | 1 | OD | Redundant CMM serial clock | |

|

|

|

| |

R_SDA | 1 | OD | Redundant CMM serial data | |

|

|

|

| |

N_HLY#[1..21] | 21 | I | Node Healthy (0 = Node is healthy) | |

|

|

|

| |

N_BDS#[1..21] | 21 | OD | Node Board Select (5 V = Node is present, drive to 0 | |

I/O | to turn node on) | |||

|

| |||

|

|

|

| |

2 | I/O | 10/100 Ethernet To Switch | ||

|

|

|

| |

2 | I/O | 10/100 Ethernet From Switch | ||

|

|

|

| |

FANTK[0..15] | 16 | I | Fan Tach Inputs | |

|

|

|

| |

FANPWM[0..3] | 4 | O | Fan Speed Control (3.3 V = ON) | |

|

|

|

| |

FANP#[0..3] | 4 | I | Fan tray present (3.3 V = fan tray is missing) | |

|

|

|

| |

PDEG#[0..7] | 8 | I | Power supply degrade | |

|

|

|

| |

PFAIL#[0..7] | 8 | I | Power supply fail | |

|

|

|

| |

PINH#[0..7] | 8 | O | Power supply inhibit | |

|

|

|

| |

STx | 1 | O | Serial transmit | |

|

|

|

| |

SRx | 1 | I | Serial receive | |

|

|

|

| |

SCTS | 1 | I | Serial clear to send | |

|

|

|

| |

SRTS | 1 | O | Serial request to send | |

|

|

|

| |

SDSR | 1 | I | Serial data set ready | |

|

|

|

|

26 | Technical Product Specification |