Channel Service Unit Includes Terminal User Interface

Copyright E 1996 Paradyne Corporation. All rights reserved

Warranty, Sales, and Service Information

Trademarks

Operators Guide 3160-A2-GB22-10

Important Safety Instructions

CC DGD D C D CC

Government Requirements and Equipment Return

United States

316x DSU/CSU Facility Interface Codes Description

Canada

Government Requirements

Table of Contents

Glossary Index

LCD

List of Figures

Slide Latch Adapter Cable Feature Number 3100-F1-560

List of Tables

Models 3160/3614 DSU/CSUs Rear Panel Connectors

Acculink 316x DSU/CSU

Reference Documents

Preface

Objectives and Reader Assumptions

Related Documents

Overview

Introduction

User Interface

Features

Alarm Interface

Integral Modem

Async Terminal Interface Support

Front Panel Access Control Feature

Front Panel Emulation

Front Panel Pass-Through

3160/3164 DSU/CSU Rear Panel

Acculink 316x DSU/CSU Physical Description

Standalone Model 3160/3164 DSU/CSUs

3160/3164 DSU/CSU Front Panel

LCD

DSU/CSU Front Panel

DSU/CSU Rear Panel

Models 3160/3164 DSU/CSUs Rear Panel Connectors

Connector Name

Function

Carrier-Mounted Model 3161 DSU/CSU

Model 3161 Front Panel Functions

Model 3161 DSU/CSU Rear Panel

Auxiliary Backplane

Planning

Installation

Network

Fractional T1

Serial Connection to Snmp

Quick Start Procedure

Box Contents

Installing the +24 Vdc Power Supply

Optional Power Selection

±48 Vdc Single Source Power Supply Pinouts

Installing the Single ±48 Vdc Power Supply

±48 Vdc Redundant Source Power Supply Pinouts

Installing the Redundant ±48 Vdc Power Supply

DSU ESF

Power-Up Self-Test

Status TStat LED ID

Selecting a Model

DSU/CSU Identity

Status DevHS STest Perf

Identity Cust ID=xxxxxxxx

Control Reset CID Password

Identity Ser=xxxxxxx

Identity Mod=xxxx-xx-xxx

Setting/Changing a Password

Establishing Access Security on a Port

Passwd Up Down Save

Control Reset CID Passwd

3160/3164 DSU/CSU Cabling

13 /3164 DSU/CSU Cabling Configurations

Installing Front Panel Emulation Software

Factory Default Configuration Options

Enabling/Disabling the Front Panel

3160/3164 DSU/CSU User Interface Access Security

Security Lvl1 Lvl2

Changing User Interface Access Security

LCD

Operation

Acculink 316x DSU/CSU

Operating the Front Panel

Model 3161 DSU/CSU Faceplate

Keypad

Device Health and Status Messages

Other Displays

Context-Sensitive Menu

LEDs

LEDs

Name Color Meaning

System LEDs

SIG

Network Interface LEDs

PDV

DSX-1 Drop/Insert Port LEDs

DTR

Data Port LEDs

DTR TXD

Displaying LED Conditions on the Front Panel

Prt1 Prt2

Selecting the DSX-1 or a Port for LED Display

LED Dsply DTE

DTE

LED Display Selection Screen

Front Panel Emulation on a PC

Front Panel Emulation Screen Icons Name Meaning

Test Jacks

12 DSU/CSU Test Jacks

Test Jack Functions

Configuring the DSU/CSU

Configuration Option Areas

Configuration Options

14. Configuration Branch for the Front Panel

Configuration Procedures

15. Configuration Branch for the Async Terminal

Displaying/Editing Configuration Options

16. Load From Screen

NET Framing ESF Next D4 ESF

Save Edit to Activ Cust

Saving Edit Changes

Selecting/Copying to a Specific Port

Selecting a Specific Port

Port Select Copy Prt1 Prt2

Prt4 Value Options

Prt1 Value Options

Prt2 Value Options

Prt3 Value Options

To Copy to One or All Ports

Copy From Prt1 Prt2 Prt3

Copy To All Prt1 Prt2

Selecting the Port

Configuring the 3160/3164 DSU/CSU for Snmp Management

Modem Use Next Snmp Ascii

Com Use Next Snmp Ascii

Setting the IP Address

System Name Next Edit Clear

Edit User Alarm

Snmp Config Gen Trap

Snmp

Selecting the Link Layer Protocol

000.000.000.000 Up Down Save

010.155.111.222 Up Down Save

Modem Link Next PPP Slip

Specifying the Community Names and Access Types

Public Up Down Save

CommunityName1 Next Edit Clear

Enterprise-Specific Trap Definitions Trap Value Event

Access Next Read R/W

Snmp Traps

Newname Up Down Save

Num Trap Mgrs1 Next

Selecting the Number of Trap Managers

23. Trap Options Screen

Configuring an IP Address for Snmp Trap Manager

Trap n IP Adr Next Edit Clear

Configuring DS0 Channels

24. Example Channel Allocation

25. Example Interface Tables

Network T1 Interface Network Channel Allocation

26. DS0 Channels Containing RBS Information Worksheet

DTE Chan Assign Voice Config N1 ± RBS or Data

NET, DTE

Port Chan Options Value Conf

Port Chan Options Value Conf

Edit Port NET Chan

Display Channel Symbols Meaning

Channel Config Dsply Clear DTE

Displaying DS0 Channel Assignments

Display Chan

NET DTE

Prt1

Allocating Data Ports

NET

Block Channel Assignment Method Example

Assign ByACAMI Next Block Acami

Acami Channel Assignment Method Example

Port Rate384 Next 64

Start AtClear Next Clear N1

Next Prt1 Prt2

Individual Channel Assignment Method Example

Assign ByChan Block Acami Chan

Assign ByChan Next Block Acami

DTE Channels Assign Voice

RBS

30. DTE Assignment Screen

Clear Channel

Clearing DS0 Channel Allocation

Timing

32. Common Clocking Configurations

Clock SrcNET Next NET DTE

Configuring for Network Timing Example

Edit NET Chan Gen

GenYellowEnab Next Enab Disab

Configuring for External Timing Example

Clock SrcNET Prt1 Int Ext

Clock Rate1544 Next 2048

Selecting the Shared Communication Port

101

Self±TestEnab Next Enab Disab

Checking the Status

Device Health and Status

MasterComDisab Next Enab Disab

Health and Status Messages

Message

Description

Auto Dev H/S OOF at DTE

Displaying Device Health and Status

Self-Test Health

Device H/S OOF at DTE

STest Health Passed

Displaying Self-Test Results

Self-Test Health Messages

Message Description

VldIntvl=xx

CurTimer

Performance Report

Event=xx,xxx

StEvnt

35. Carrier Telco and User Register Organization

Displaying User Performance Registers

36. Telco Performance Report Screen

Clearing User Performance Registers

LED

Controlling the DSU/CSU

DSU Fmt

Acquiring/Releasing the Active Physical Interface

Acquiring the Active Physical Interface

Releasing the Active Physical Interface

Using the Integral Modem

Initiating a Call for Front Panel Pass-Through Operation

Ft. Panel Released

Call Setup Pass Dial ChDir

Pass n Up Down Dial

Dial n Up Down Dial

Passwd Up Down Done

Entering a Password to Gain Access

Call Setup Disc ChDir

Disconnecting the Modem Connection

Disconnecting Using the Disconnect Command

Disconnecting Using Front Panel Keys

Xxxxxxxxxxxxxxxxx Next Prev Edit

Entering Numbers in the Phone Directories

Valid Phone Number Characters Meaning Restrictions

Xxxxxxxxxxxxxxxxx Up Down Save

Control ACO Rel LED

Deactivating the Alarm Relay

Alarm Cut-Off Command Complete

Starting Front Panel Emulation

Setting Interface Options

Using the Async Terminal Feature

Async Terminal Menus and Screens

Entering a Password

Activating Interface Option Changes

Initiating an Async Terminal Session

Edit and Display Screens

Menu Selection Screens

Function Representations for Edit Screens Function Key Usage

Hard-Key Representations for Edit Screens Usage

Terminating a Session

Troubleshooting

Maintenance

Interface Snmp Trap Meaning

Alarms

Snmp Traps

Snmp Trap per Interface

Test Branch

Test Commands

Rem Loopback

Remote Loopback Tests

Sending a Line Loopback Up or Down

Test Rlpbk Lpbk Ptrns

Sending a V.54/ANSI FT1 Activation/Deactivation

Local Loopback Tests

Rem Loop Type Prt1 Prt2 Prt3

Starting a Line Loopback

Valid Loopback Combinations

Loopback Abort LLB PLB

Starting a DTE Loopback

Starting a Payload Loopback

Starting a Repeater Loopback

Loopback

LLB PLB DLB

Loopback Dclb Prt1 Prt2 Prt3

Starting a Data Channel Loopback

PLB DLB RLB

DLB RLB Dclb

Starting a Data Terminal Loopback

RLB Dclb Dtlb

Loopback Dtlb Prt1 Prt2 Prt3

LLB PLB

DTE-initiated Loopbacks

Aborting Loopbacks

Loopback Abort All

Sending Test Patterns

Test Patterns

Monitor Name NET Prt1 Prt2

Monitoring Test Patterns

8 Network Port

Patterns Mon Qrss

Patterns Abort All Send Mon

Aborting Test Patterns

Lamp Test

Starting a Lamp Test

0123456789 = ?

Aborting a Lamp Test

Test Lpbk Ptrns Lamp

Lamp Test Abort Start

Test Status Messages

Displaying DSU/CSU Test Status

Resetting the DSU/CSU

Downloading Software

Status STest Perf TStat

Device Reset Yes No

Control ClrUsr Reset

Front Panel Menu a

3160-A2-GB22-10

Front Panel Menu

Power Requirements

Technical Specifications B

Clocking Sources

Power Consumption Dissipation

Pounds .82 kg

Functional Grouping

Configuration Options C

DTE Interface Configuration Options

Table C-1 DTE Interface Configuration Options

Context-Sensitive Menu

Send Ones Enab Next Enab Disab Prev

Extrn DLB Disab Next Enab Disab Prev

Port Type E530 Factory Next E530 V.35 RS449 Prev

Port Configuration Options

Port Configuration Options

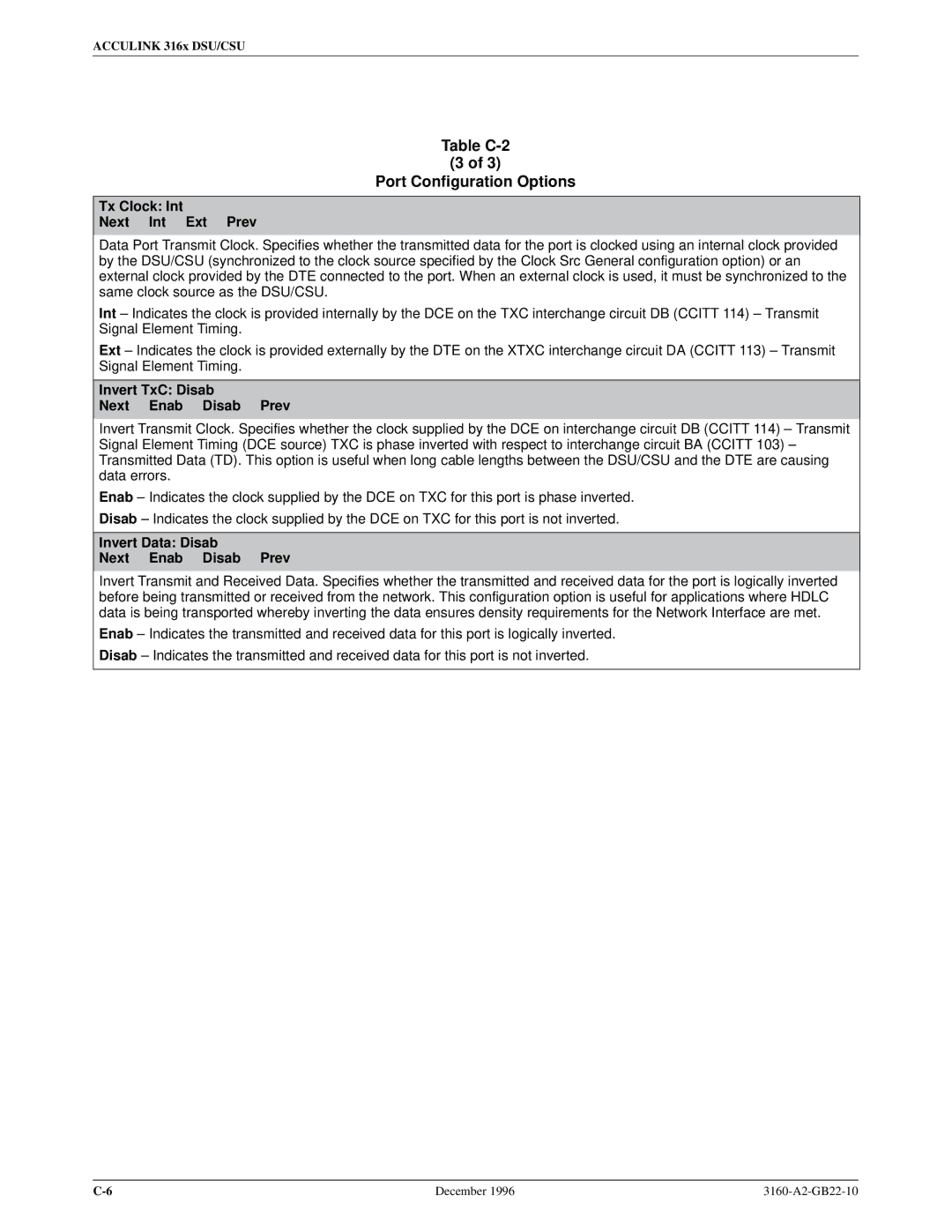

Table C-2

Table C-2 Port Configuration Options

All Ones Both Next Disab DTR RTS Both Prev

Rcv Yellow Halt Next None Halt Prev

Tx Clock Int Next Int Ext Prev

Invert TxC Disab Next Enab Disab Prev

Invert Data Disab Next Enab Disab Prev

Table C-3 Network Interface Configuration Options

Network Interface Configuration Options

Bit Stuff Next 62411 Part68 Disab Prev

NET PLB Enab Next Enab Disab Prev

Table C-4 DTE Channel Configuration Options

Channel Configuration Options

Table C-5 Data Port Channel Configuration Options

N10 N11 N12 N24 Next Prev D10 D11 D12 D24

Start At Clear Next N10 N11 N24 Prev D10 D11 D24

Clock Src NET Next NET DTE Prt1 Int Ext Prev

General Configuration Options

Table C-6 General Configuration Options

Gen Yellow Enab Next Enab Disab Prev

Table C-7 User Interface Configuration Options

User Interface Configuration Options

Com Clk Int Next Int Ext Prev

MasterComDisab Next Enab Disab Prev

Com Use Ascii Next Snmp Ascii Term Prev

Com Type Async Next Async Sync Prev

CStop Bits Next 1 1.5 2 Prev

Com Rate Next 1.2 2.4 4.8 9.6 14.4 19.2 Prev

Char Length Next 7 8 Prev

CParity None Next None Even Odd Prev

MParity None Next None Even Odd Prev

Modem Type Async Next Async Sync Prev

Modem Rate Next 1.2 2.4 Prev

MChar Len Next 7 8 Prev

Snmp Trap Disab Next Enab Disab Prev

Alarm Configuration Options

Table C-8 Alarm Configuration Options

Alrm Msg Disab Next Disab Modem Com Both Prev

Next None 1 2 3 4 5 Prev

Dial Delay Next 1 2 3 4 5 6 7 8 9 10 Prev

DialOut Disab Next Enab Disab Prev

Call Retry Disab Next Enab Disab Prev

AlrmRelay Disab Next Enab Disab Prev

Err Rate 10E-4 Next 10E-4 10E-5 10E-6 10E-7 10E-8 10E-9 Prev

Table C-9 General Snmp Configuration Options

Snmp Configuration Options

Modem IP Adr Clear Next Edit Clear Prev

Access 2 Read Next Read R/W Prev

Com IP Adr Clear Next Edit Clear Prev

Com Link PPP Next PPP Slip Prev

Gen Trap Both Next Disab Warm Auth Both Prev

Table C-10 Snmp Trap Configuration Options

Num Trap Mgrs Next 1 2 3 4 5 6 Prev

Trap n IP Adr Clear Next Edit Clear Prev

Trap I/F All Next NET DTE T1s Ports All Prev

Link Trap Both Next Disab Up Down Both Prev

T1 Network Connector Interface

Pin Assignments D

Cables

Receiver Ring Receiver Tip Transmitter Ring Transmitter Tip

RJ48C DA15P

DSX-1 Port DTE Interface

Integral Modem Service Port Interface

AUX Port Interface

COM Port Interface

Figure D-5. COM Port-to-PC Cable Feature Number 3100-F1-550

Acculink 316x DSU/CSU

EIA-530A DB25 Port Interface Connector

Table D-7 EIA-530A Port Interface Connector Signal Circuit

Direction Pin Mnemonic Number

Table D-8 RS449 Port Interface Connector Signal Circuit

RS449 Port Interface Connector

Pin Assignments

Port Interface Connector

Table D-9 Port Interface Connectors Signal

Direction Pin Number

Pin Assignments

Power Cable

Power Input Connector

Table D-10 DC Power Connector Signal Pin Number

External Clock Connector

Slide Latch Adapter

Figure D-11. The connector information is in Table D-12

Snmp MIB Objects E

System Group Supported

Management Information Base MIB II RFC

System Group ± ªsysObjectIDº Object system

System Group ± ªsysServicesº Object system

System Group, MIB

System Group ± ªsysDescrº Object system

Interface Group ± ªifMtuº Object ifEntry

Interface Group, MIB

Interface Group ± ªifDescrº Object ifEntry

Interface Group ± ªifTypeº Object ifEntry

DTE

Interface Group ± ªifAdminStatusº Object ifEntry

IP Group, MIB

IP Group ± ªipNetToMediaTableº Object ip

Icmp Group, MIB

UDP Group, MIB

DS1/E1 MIB RFC

Near End Group ± ªdsx1SendCodeº Object dsx1ConfigEntry

Near End Group ± ªdsx1LineStatusº Object dsx1ConfigEntry

Near End Group ± ªdsx1SignalModeº Object dsx1ConfigEntry

Near End Group ± ªdsx1Fdlº Object dsx1ConfigEntry

DS1 Fractional Group, DS1/E1 MIB

RS-232-like MIB RFC

Near End Group ± The DS1 Total Table Objects dsx1TotalEntry

Far End Group, DS1/E1 MIB

General Port Table ± ªrs232PortTypeº Object rs232PortEntry

Number of Ports ± ªrs232Numberº Object rs232

General Port Table, RS-232-like MIB

General Port Table ± ªrs232PortIndexº Object rs232PortEntry

Input Signal Table ± ªrs232InSigChangesº rs232InSigEntry

Input Signal Table, RS-232-like MIB

Input Signal Table ± ªrs232InSigNameº rs232InSigEntry

Input Signal Table ± ªrs232InSigStateº rs232InSigEntry

Generic-Interface MIB Extensions RFC

Output Signal Table ± ªrs232OutSigNameº rs232OutSigEntry

Output Signal Table ± ªrs232OutSigStateº rs232OutSigEntry

Output Signal Table ± ªrs232OutSigChangesº rs232OutSigEntry

Acculink 316x DSU/CSU

Troubleshooting Table F

Table F-1 Troubleshooting Symptom Possible Cause Solutions

Yellow at Net

Yellow at DTE

AIS at Net

AIS at DTE

Configuration Worksheets G

Net Value Options

DTE

Configuration Worksheets

Network T1 Interface Network Channel Allocation

D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D25

Acami

Port Chan Options Value Conf

Snmp Gen Value Options

Alarm Value Options

General Options Value

User Options Value

Cable numbers for DSU/CSU are located

Equipment Feature Number

Equipment List H

PEC Code

AIS

Glossary

EER

Index

DTE

Index

Index-4