OTS

USA

Warranty

Page

Table of Contents

Reference

Analysis SONET/T1M1 Analysis SDH/G.826

Iii

Appendices

SOURceDATAPAYLoadBACKgroundPATTern

General Safety Summary

How to Avoid Fire or Personal Injury

General Safety Summary

Keep Product Surfaces Clean and Dry

Terms in this Manual

Safety Terms and Symbols

Symbols on the Product

Terms on the Product

General Safety Summary Viii

Preface

How This Manual is Organized

Conventions

Getting Started

Product Description

OTS9100 Features and Capabilities

Getting Started

OTS91L4 Standard

Accessories

Standard with each shipment

OTS91L5 Standard

OTS91R2 Standard

OTS91L7 Standard

OTS91L8 Standard

OTS91T3 Standard

International Power Plug Options Chassis Only

Adapters, SMA

OTS9100 Installation

First Operation

Removing Cards

Slot Positioning of OTS Cards

Multiple Modules

OTS9000 with card slot assignment

Module Card Interconnection

Power On and Software Initialization

Proper location Interconnection cables

Receiver Setup

Transmitter Setup

Module Quick Check

Getting Started

Shutdown and Power Off

Emergency Startup Disk

Front Panel Indicators and Connectors

OTS9100 Front Panel

Module OK

10Gb/s Transceiver Optics

Optical OUT

Tx Data

Optical

Rx Data OUT

Appropriate circuit. -3 1550 nm Transceiver Front Panel

Laser Lockout, Remote Interlock

Receive Analysis

Defect indicator will turn off when a new test is started

Module OK

Rx Data

Rx Event OUT

Rx Clock OUT

Tx Event OUT

Transmit Generation

Transmit Front Panel

Tx Data OUT

MHz Trig OUT

GHz Clock

GHz Trig OUT

Clock Trigger

MHz External Clock

Rx Clock

GHz Clock Out

Software Interface Operating Basics

Elements of the User Interface

System

Task Bar

Menu Bar

View

Multiple Window Mode View

Single Mode

Multiple Mode

Window

Tool Bar

Laser Control Bar

Main Status Bar

Error

Test Control Bar

Client Lockout

Laser Off

Test

Frame Grabbers

LED Window

User Selected Signal LED Window

Module Signal Summary LED Panel

Slot Signal LED Panel

Clear History

Module LED Panel

LED Module Display

Description of Status Window Virtual LED Indicators

SEF OOF

Select Signal User Selected Signal Slot Signal

LED Display Selection

Navigation Window

Scroll Buttons

Summary Icons

Setup Property Menus

Signal Standard

10 Transmitter Setup Signal menu

Timing Source

Bert Mode

Signal Source

Trigger Output

Packet Over Sonet POS

SPE/VC3 Stuff Column Control

Background Channels

Transmitter Transport Overhead

11 Transmitter Transport Overhead menu

Edit Overhead

12 Edit Overhead dialog box

Through Mode

13 Through Mode Overwrite menu

J0 Multi-Byte Trace

14 Transmitter J0 Trace dialog box

Transmitter Path Overhead

16 Transmitter Path Overhead Property Menu

Path Through Mode

Edit Path Overhead

J1 Multi-Byte Trace

19 Transmitter J1 Trace dialog box

Transmitter Error Insertion

21 Transmitter Error Insertion menu

Anomaly Insertion and Through Mode

Anomaly Insertion

23 Defect Insertion of the Error Insertion menu

Defect Insertion

Transmitter K1, K2 Decode

24 Transmitter K1, K2 Decode menu

25 Edit K1, K2 Bytes dialog box

Operating Basics User Interface

IP Setup

Transmitter IP Payload

IP Header

Transmitter IP Error Insertion

Error Selection

Current Error Insertion

Receiver Signal

26 Receiver Setup Signal menu

Signal Structure

Test Pattern

Receiver Threshold Offset

27 Receiver Threshold Offset dialog box

28 Receiver Setup Trace Mismatch menu

Receiver Trace Mismatch

Edit C2 Byte

29 J0 Trace Editor dialog box

31 Edit C2 dialog box

Hpplm and HP Unequipped Detection

Receiver IP Setup

Setup Summary

32 Setup Summary menu

Signal Monitor Menus

Receiver Transport Overhead

RS Trace Section Trace J0

S1 Synchronization Status

35 Signal Monitor Path Overhead

Receiver Path Overhead

Path Trace J1

C2 Status

36 Signal Monitor K1,K2 Decode

Receiver K1,K2 Decode

37 Signal Monitor Payload

Receiver Payload

Test Control Menu

39 Test Control Parameters dialog box

Test Control Summary

40 Test Control Summary menu

Measurements Menu

Receiver Real-Time

42 Real-Time menu Path display

Receiver Cumulative

44 Cumulative Measurements Display Section and Line

45 Cumulative Measurements Display Path

Receiver History

46 Example of Results History Data Section/Line

47 Example of Results History Data -Path

Operating Basics User Interface

Receiver IP Measurements

Receiver IP Measurements display

Transmitter IP Measurements

Analysis Menu

Analysis SONET/T1M1

49 Analysis menu SONET/T1M1 Path

Analysis SDH/G.826

50 Analysis menu SDH/G.826 RS/MS

51 Analysis menu SDH/G.826 Path

APS Measurements Menu

52 APS Measurements menu

53 Set APS Test Parameters dialog box

54 Copy APS Measurement Data dialog box

Remote Access Setups

Select Server

Display Notation

59 View Options dialog box

Display Configuration

Server System

System View

Scpi Output

63 View Scpi Output dialog box

Results Files

Results File Management

64 Results File Management dialog box

Opening files on the local computer

ResultsViewer

Operation

On the Local computer

Connecting to an OTS System Viewing results files

65 Cumulative Results screen of the ResultsViewer

Printing results data

Configuring ResultsViewer

Selecting and arranging windows

Exporting test data to other programs

Sample output of data from a test results file

A202

A604

Record type codes

Summary report Test file info

Sonet GR-253 Line Analysis

History data

Configuring the exported data

66 Configure Data Report dialog box

Logging

Starting the Event Printer program

Select Events

Copy to Printer

Copy to Clipboard

Copy to File

Clear

Muting Event Printer behavior with continuous events

Configuring a printer in Windows

Minimizing the Event Printer window

102

Ieee 488.2 System Commands

Commands Overview

Remote Control Setup and Format Commands

Remote Control Lockout

Remote Control Port Settings

System Configuration Queries

Receiver Commands OTS9100 module

Save and Restore System Settings

System Signal Standard OTS9100 module

System File Management

Receiver Signal Analysis Commands OTS9100 module

Receiver Signal Measurement Commands OTS9100 module

Receiver Test Control OTS9100 module

Transmitter Commands OTS9100 module

Syntax

Ieee 488.2 Common Commands

Command and Query Structure

Description

Block Format

Hex Block Format

Query format

Scpi Commands and Queries

Command Format

Example

Parameter types and formats

Sourcedatapayloadpattern Enum

Optional and alternative parameters

#216ABCDEFGHIJKLMNOP

Minimum information needed

Abbreviating Commands, Queries, and Parameters

Controlling Responses to Queries

Accepted short form

Chaining Commands and Queries

Example of chaining commands and queries

General Rules

Slot Specifiers

Command Description

ESE

OPC

SENSeANALysisG826AMSFAR

SENSeANALysisG826AMSFARALL

SENSeANALysisG826AMSNEARALL

SENSeANALysisG826AMSNEAR

SENSeANALysisG826APATHFAR

SENSeANALysisG826APATHNEAR

SENSeANALysisG826APATHFARALL

SENSeANALysisG826APATHNEARALL

SENSeANALysisG826ARSALL

SENSeANALysisG826ARS

SENSeANALysisGR253ALINEFAR

SENSeANALysisGR253ALINENEAR

SENSeANALysisGR253ALINEFARALL

SENSeANALysisGR253ALINENEARALL

SENSeANALysisGR253APATHFAR

SENSeANALysisGR253APATHFARALL

SENSeANALysisGR253APATHNEAR

SENSeANALysisGR253APATHNEARALL

SENSeANALysisGR253ASECTionALL

SENSeANALysisGR253ASECTion

SENSeANALysisPATHHPPLM

SENSeANALysisPATHLABElEXPEcted

SENSeANALysisPATHHPPLMGENEric

SENSeANALysisPATHHPUNEQ

SENSeANALysisPATHTRACeEXPEcted

SENSeANALysisPATHTRACeEXPEctedVALUe

SENSeANALysisPATHTRACeEXPEctedTYPE

SENSeANALysisPATHTRACeEXPEctedVALUeSTRIng

SENSeANALysisSECTionTRACeEXPEcted

SENSeANALysisPATHTRACeTIM

SENSeANALysisSECTionTRACeEXPEctedTYPE

SENSeANALysisSECTionTRACeTIM

SENSeANALysisSECTionTRACeEXPEctedVALUe

SENSeANALysisSECTionTRACeEXPEctedVALUeSTRIng

SENSeDATAAUTOscanSTRUcture

SENSeDATAIPPAYLoadPATTernUDATA

SENSeDATACHANnel

SENSeDATAIPPAYLoadPATTern

SENSeDATAIPSTReamINDEX

SENSeDATAPATHTRACeVALUeSTRIng

SENSeDATAPATHTRACeTYPE

SENSeDATAPATHTRACeVALUe

SENSeDATAPAYLoadPATTern

SENSeDATAPOHBYTE

SENSeDATAPAYLoadPATTernUDATA

SENSeDATAPOHALL

SENSeDATAPOHBYTEC2A

SENSeDATASECTionTRACeTYPE

SENSeDATARATE

SENSeDATASECTionTRACe

SENSeDATASECTionTRACeVALUe

SENSeDATATOHSTM1AALL

SENSeDATASPESTUFfing

SENSeDATASTRUcture

SENSeDATATOHSTS1AALL

SENSeINPutTHResholdLOS

SENSeINPUtTHREshold

SENSeMEASureAPSTimeCONDition

SENSeMEASureAPSTimeMAXTime

SENSeMEASureAPSTimeRUN

SENSeMEASureAPSTimeDETEcted

SENSeMEASureAPSTimeSTATus

SENSeMEASureHDLCFRAMes

SENSeMEASureAPSTimeTHREshold

SENSeMEASureAPSTimeVALUe

SENSeMEASureHDLCFRAMesALL

SENSeMEASureIPPACKetsALL

SENSeMEASureHDLCBYTes

SENSeMEASureIPPACKets

SENSeMEASureLINECUMUlative

SENSeMEASureLINEWINDowALL

SENSeMEASureLINEWINDow

SENSeMEASurePATHCUMUlative

SENSeMEASurePATHWINDow

SENSeMEASurePATHCUMUlativeALL

SENSeMEASurePATHWINDowALL

SENSeMEASureSECTionCUMUlativeALL

SENSeMEASureSECTionCUMUlative

SENSeMEASureSECTionWINDow

SENSeMEASureWINDowLEVEL

SENSeMEASureSECTionWINDowALL

SENSeMEASureWINDowCLEAR

SENSeMEASureWINDowSIZE

SENSeOPTicalTHResholdAUTO

SENSeSIGNalSTANdard

SENSeOVERheadMONItorCHANnel

SENSeSTATusLEDSHEXadecimal

SENSeSTATusLEDS

SENSeSTATusLEDSNUMEric

SENSeSTATusPATHLEDSHEXadecimal

SENSeSTATusPATHLEDS

SENSeSTATusPATHLEDSNUMEric

SENSeTESTSTATe

SENSeTESTDESCription

SENSeTESTMODE

SENSeTESTTIME

SOURceCLOCkSOURce

SENSeTESTTIMEELAPsed

SENSeTRIGgerMODE

SOURceDATABACKgroundSTRUcture

SOURceDATAHDLCIFRameGAP

SOURceDATACHANnel

SOURceDATACHANnelREPLicate

SOURceDATAIPHEADerADDRessDEST

SOURceDATAIPHEADerID

SOURceDATAIPHEADerFLAG

SOURceDATAIPHEADerFRAGOFFSet

SOURceDATAIPHEADerPROTocol

SOURceDATAIPHEADerVERSion

SOURceDATAIPHEADerTSERVice

SOURceDATAIPHEADerTTLive

SOURceDATAIPPAYLoadPATTern

SOURceDATAPOSSCRambling

SOURceDATAIPSTReamINDEX

SOURceDATAIPTRAFfic

SOURceDATAOVERheadPASSthru

SOURceDATAPARItyLOOP

SOURceDATAOVERheadPASSthruALL

SOURceDATAPATHOVERheadPASSthru

SOURceDATAPATHTRACe

SOURceDATAPATHOVERheadPASSthruALL

SOURceDATAPATHTRACeTYPE

SOURceDATAPATHTRACeVALUeSTRIng

SOURceDATAPATHTRACeVALUe

SOURceDATAPAYLoadBACKgroundPATTern

SOURceDATAPAYLoadPATTern

SOURceDATAPAYLoadBACKgroundPATTernUDATA

SOURceDATAPAYLoadPATTernUDATA

SOURceDATAPOHBYTE

SOURceDATAPOHALL

SOURceDATAPOHBACKgroundBYTEC2A

SOURceDATAPOHBYTEC2A

SOURceDATASECTionTRACe

SOURceDATAPOHDEFAult

SOURceDATARATE

SOURceDATASECTionTRACeTYPE

SOURceDATASOURce

SOURceDATASECTionTRACeVALUe

SOURceDATASECTionTRACeVALUeSTRIng

SOURceDATASPEBACKgroundSTUFfing

SOURceDATATOHSTS1AALL

SOURceDATASPESTUFfing

SOURceDATASTRUcture

SOURceDATATOHSTS1ABYTE

SOURceINSErtANOMalyRATE

SOURceDATATOHSTS1ADEFAult

SOURceINSErtANOMalyMODE

SOURceINSErtANOMalyRATERANGe

SOURceINSErtANOMalySTATe

SOURceINSErtANOMalyREPLicateB2A

SOURceINSErtANOMalyTYPE

SOURceINSErtDEFEctSTATe

SOURceINSErtDEFEctMODE

SOURceINSErtDEFEctTIME

SOURceINSErtDEFEctTYPE

SOURceINSErtDEFEctTIMERANGe

SOURceINSertIPANOMalyMODE

SOURceINSertIPANOMalyTYPE

SOURceINSertIPANOMalyRATE

SOURceINSertIPANOMalyRATERANGe

SOURceMEASureHDLCBYTes

SOURceMEASureIPPACKets

SOURceMEASureHDLCFRAMes

SOURceMEASureHDLCFRAMesALL

SOURceMEASureIPPACKetsALL

SOURceOUTPutLASerINFOSERial

SOURceSIGNalSTANdard

SOURceOUTPutLASerINFOOPTion

SOURceOUTPutLASerINFOWAVelength

SYSTemCOMMunicateGPIBPRIMary

STATusPRESet

SOURceTRIGgerMODE

SYSTemCOMMunicateGPIBSECOndary

SYSTemCOMMunicateNETWorkPROMpt

SYSTemCOMMunicateNETWorkECHO

SYSTemCOMMunicateNETWorkIPPORT

SYSTemCOMMunicateNETWorkRXTERM

SYSTemCOMMunicatePORTECHO

SYSTemCOMMunicateNETWorkTXTERM

SYSTemCOMMunicatePORTPROMpt

SYSTemCOMMunicatePORTTXTERM

SYSTemCOMMunicatePORTRXTERM

SYSTemCOMMunicateSERIalCOM1ADTR

SYSTemCOMMunicateSERIalCOM1AECHO

SYSTemCOMMunicateSERIalCOM1AENABle

SYSTemCOMMunicateSERIalCOM1AFLOW

SYSTemCOMMunicateSERIalCOM1ANSTOP

SYSTemCOMMunicateSERIalCOM1ANDATA

SYSTemCOMMunicateSERIalCOM1APARIty

SYSTemCOMMunicateSERIalCOM1ARTS

SYSTemCOMMunicateSERIalCOM1APROMpt

SYSTemCOMMunicateSERIalCOM1ARATE

SYSTemCOMMunicateSERIalCOM1ARXTERM

SYSTemCOMMunicateSERIalCOM2ADTR

SYSTemCOMMunicateSERIalCOM2AENABle

SYSTemCOMMunicateSERIalCOM1ATXTERM

SYSTemCOMMunicateSERIalCOM2AECHO

SYSTemCOMMunicateSERIalCOM2ANDATA

SYSTemCOMMunicateSERIalCOM2AFLOW

SYSTemCOMMunicateSERIalCOM2ANSTOP

SYSTemCOMMunicateSERIalCOM2APROMpt

SYSTemCOMMunicateSERIalCOM2APARIty

SYSTemCOMMunicateSERIalCOM2ARATE

SYSTemCOMMunicateSERIalCOM2ARXTERM

SYSTemCONFigMODuleSERIAL

SYSTemCOMMunicateSERIalCOM2ARTS

SYSTemCOMMunicateSERIalCOM2ATXTERM

SYSTemCONFigMODuleVERSion

SYSTemCONFigMODuleTYPE

SYSTemCONFigMODuleVARIANT

SYSTemCONFigSLOTs

SYSTemFILEsMGMTRESUltsCOUNt

SYSTemERRor

SYSTemFILEsMGMTRESUltsAGE

SYSTemFILEsMGMTRESUltsDESTination

SYSTemFILEsMGMTRESUltsINTErval

SYSTemFILEsMGMTRESUltsENABle

SYSTemFILEsMGMTRESUltsPERcent

SYSTemFORMatBLOCk

SYSTemFILEsMGMTRESUltsSORT

SYSTemFILEsMGMTRESUltsTOTAlsize

SYSTemHEADers

SYSTemLOCKRELeaseFORCE

SYSTemSIGNalSTANdard

SYSTemLOCKRELease

SYSTemLOCKREQuest

SYSTemVERBose

TST

Reference Remote Commands ~ Command Description

Dimensions

Environmental Specifications

Temperature Ranges

Weight

Internal Mode

Transmitter Specifications

Signal Generation

Clock Source

Table A-2 SDH Default Overhead Regenerator

Through Mode

Multiplexer

Active Channel

Internal Payload Structures

Test Patterns

Background Channel

Overhead Manipulation Specifications

Error Injection

Defect/ Alarm Generation

Table A-3 Error Rate Max/Min

Alarms Detection

Receiver Analyzer Specifications

Measurements

Overhead Display

Transmitter Input and Output Specifications

OTS91L7, OTS91L8 Signal Name 9.95238 Gb/s Optical Input

Specifications

Frame Sync Output

Event Trigger Output

Transmitter Data Output Electrical

MHz Trigger Output

External 155.52 MHz Clock Input

GHz Clock Input

RX Clock Input

GHz Clock Output

RX Clock Output

Receiver Input and Output Specifications

RX Data Input

Signal Name Rx Data Out / Rx Data

Module Interconnect Specifications

Signal Name Tx Data Out / Tx Data

Signal Name Rx Data Out / 10GHz/s Data

CE Mark Compliance

Laser Safety

Certifications and Compliance

EMC Compliance Directive

Optical Card Front Panel Descriptions

Optical OUT

Tx Data

Laser Lockout, Remote Interlock

Optical

Rx Data OUT

10 Gb/s TRANSMIT-ONLY Optics Card L5-15, L5-13

Tx Data

10Gb/s Optical RECEIVE-ONLY L6

Module OK

10Gb/s Optical Transceiver Interface

External Laser L7

External Laser

10Gb/s Opticaltransmit ONLY/ External Laser L8

Figure B-5 shows the Optical Transmitter card front panel

External Laser

Accessing Help Files

Emergency Startup Disk

Emergency Startup Disk

List of Acronyms

List of Acronyms

Module Card Replacement

Tektronix Part Number Description

Module Card Replacement

Installing the Software

Installing the Software

Appendix

Illustrations of cabled OTS9100 module

Cabling OTS9100 Module to OTS9261 Tunable Laser

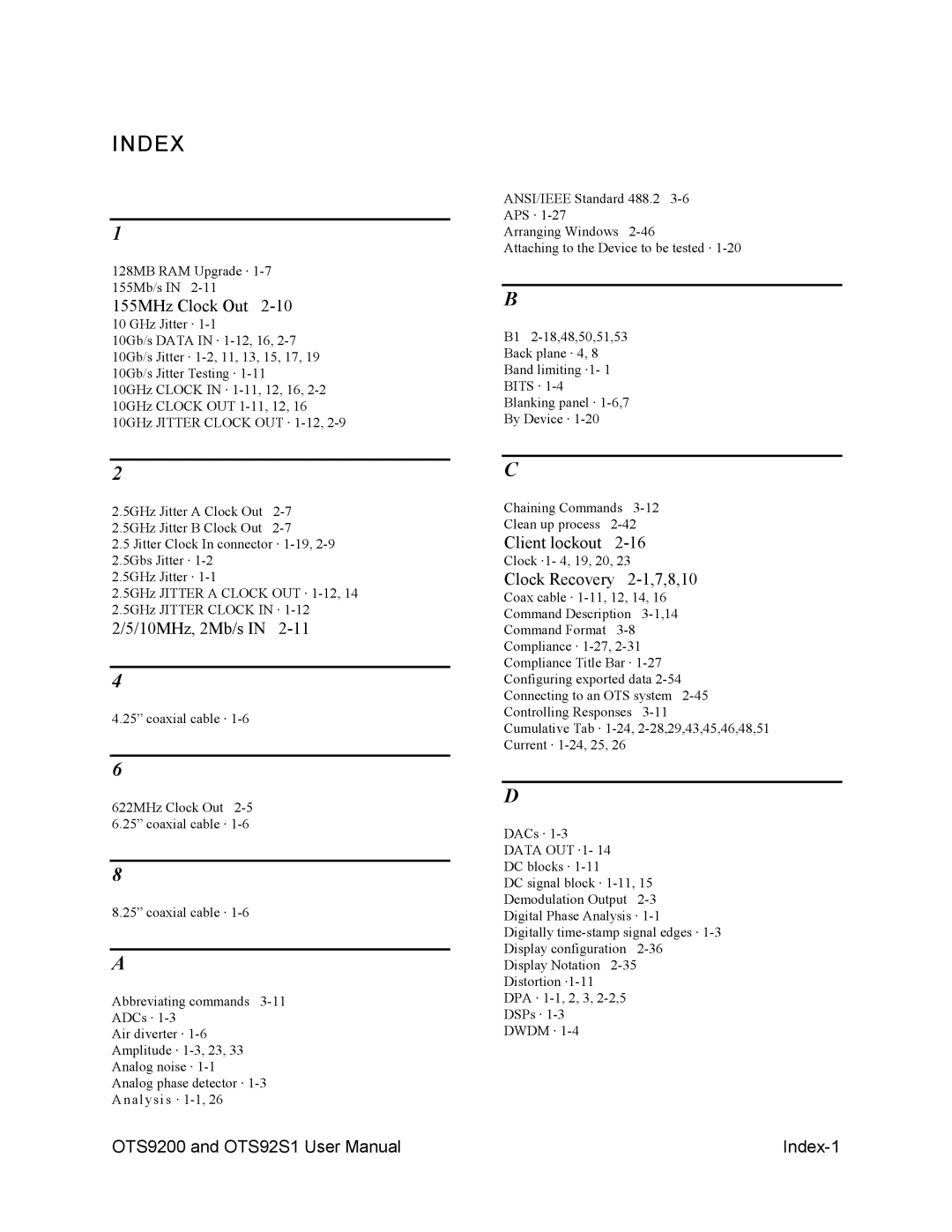

Index

Index

Index-3

Index-4