Chapter 11: Constraining the Core

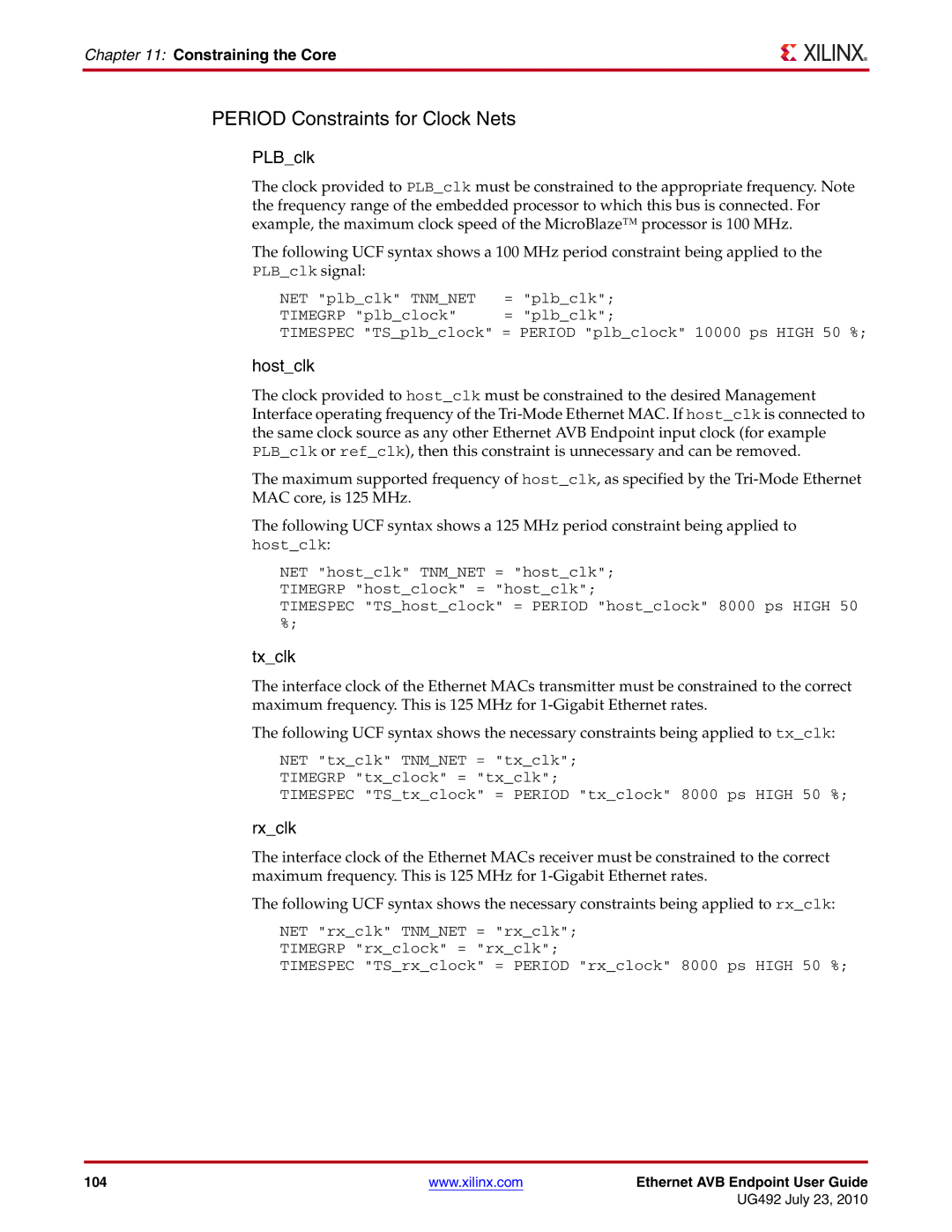

PERIOD Constraints for Clock Nets

PLB_clk

The clock provided to PLB_clk must be constrained to the appropriate frequency. Note the frequency range of the embedded processor to which this bus is connected. For example, the maximum clock speed of the MicroBlaze™ processor is 100 MHz.

The following UCF syntax shows a 100 MHz period constraint being applied to the

PLB_clk signal:

NET "plb_clk" TNM_NET | = | "plb_clk"; |

TIMEGRP "plb_clock" | = | "plb_clk"; |

TIMESPEC "TS_plb_clock" = PERIOD "plb_clock" 10000 ps HIGH 50 %;

host_clk

The clock provided to host_clk must be constrained to the desired Management Interface operating frequency of the

The maximum supported frequency of host_clk, as specified by the

The following UCF syntax shows a 125 MHz period constraint being applied to host_clk:

NET "host_clk" TNM_NET = "host_clk"; TIMEGRP "host_clock" = "host_clk";

TIMESPEC "TS_host_clock" = PERIOD "host_clock" 8000 ps HIGH 50 %;

tx_clk

The interface clock of the Ethernet MACs transmitter must be constrained to the correct maximum frequency. This is 125 MHz for

The following UCF syntax shows the necessary constraints being applied to tx_clk:

NET "tx_clk" TNM_NET = "tx_clk";

TIMEGRP "tx_clock" = "tx_clk";

TIMESPEC "TS_tx_clock" = PERIOD "tx_clock" 8000 ps HIGH 50 %;

rx_clk

The interface clock of the Ethernet MACs receiver must be constrained to the correct maximum frequency. This is 125 MHz for

The following UCF syntax shows the necessary constraints being applied to rx_clk:

NET "rx_clk" TNM_NET = "rx_clk";

TIMEGRP "rx_clock" = "rx_clk";

TIMESPEC "TS_rx_clock" = PERIOD "rx_clock" 8000 ps HIGH 50 %;

104 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |