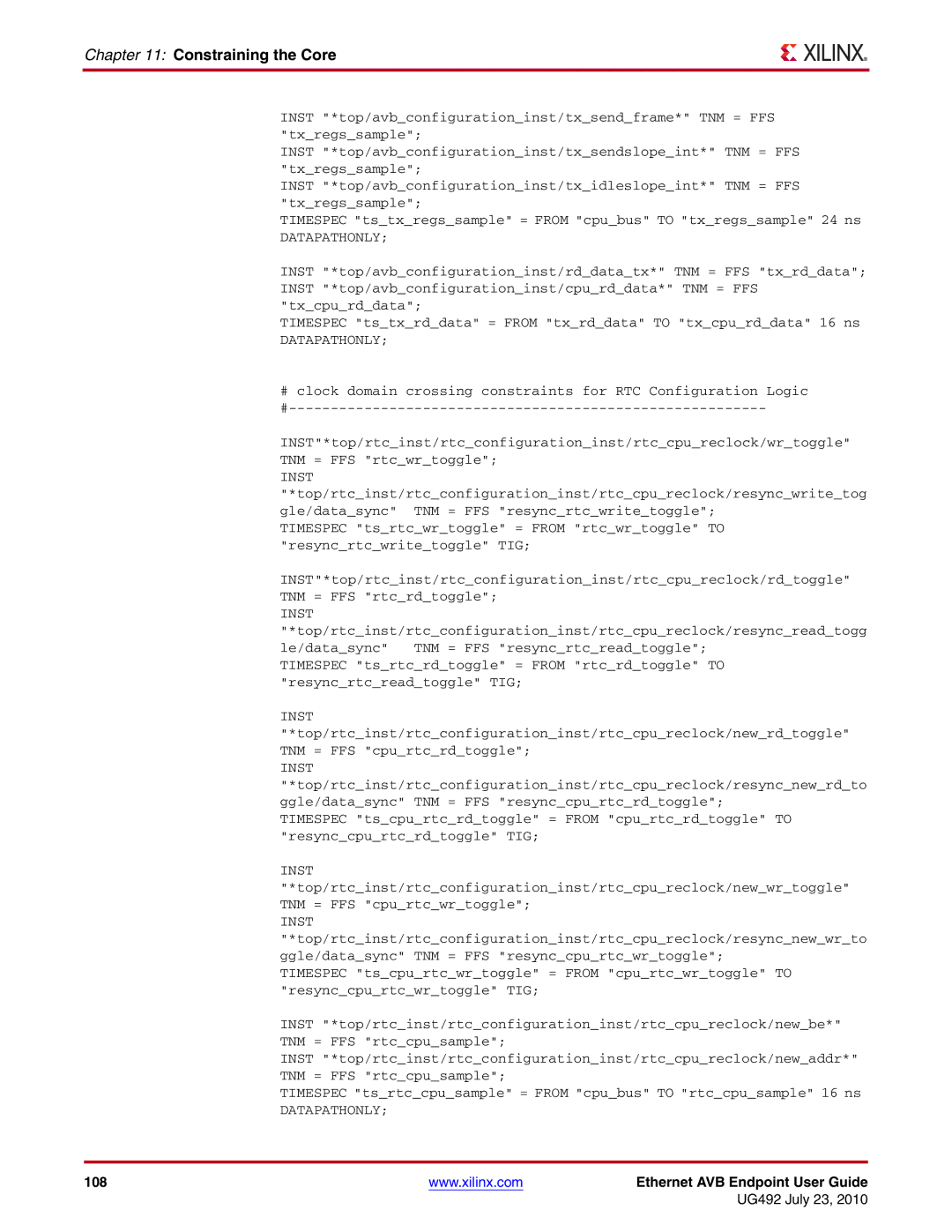

Chapter 11: Constraining the Core

INST "*top/avb_configuration_inst/tx_send_frame*" TNM = FFS "tx_regs_sample";

INST "*top/avb_configuration_inst/tx_sendslope_int*" TNM = FFS "tx_regs_sample";

INST "*top/avb_configuration_inst/tx_idleslope_int*" TNM = FFS "tx_regs_sample";

TIMESPEC "ts_tx_regs_sample" = FROM "cpu_bus" TO "tx_regs_sample" 24 ns

DATAPATHONLY;

INST "*top/avb_configuration_inst/rd_data_tx*" TNM = FFS "tx_rd_data"; INST "*top/avb_configuration_inst/cpu_rd_data*" TNM = FFS "tx_cpu_rd_data";

TIMESPEC "ts_tx_rd_data" = FROM "tx_rd_data" TO "tx_cpu_rd_data" 16 ns

DATAPATHONLY;

#clock domain crossing constraints for RTC Configuration Logic

INST"*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/wr_toggle" TNM = FFS "rtc_wr_toggle";

INST

"*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/resync_write_tog gle/data_sync" TNM = FFS "resync_rtc_write_toggle";

TIMESPEC "ts_rtc_wr_toggle" = FROM "rtc_wr_toggle" TO "resync_rtc_write_toggle" TIG;

INST"*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/rd_toggle" TNM = FFS "rtc_rd_toggle";

INST

"*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/resync_read_togg le/data_sync" TNM = FFS "resync_rtc_read_toggle";

TIMESPEC "ts_rtc_rd_toggle" = FROM "rtc_rd_toggle" TO "resync_rtc_read_toggle" TIG;

INST

"*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/new_rd_toggle" TNM = FFS "cpu_rtc_rd_toggle";

INST

"*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/resync_new_rd_to ggle/data_sync" TNM = FFS "resync_cpu_rtc_rd_toggle";

TIMESPEC "ts_cpu_rtc_rd_toggle" = FROM "cpu_rtc_rd_toggle" TO "resync_cpu_rtc_rd_toggle" TIG;

INST

"*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/new_wr_toggle" TNM = FFS "cpu_rtc_wr_toggle";

INST

"*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/resync_new_wr_to ggle/data_sync" TNM = FFS "resync_cpu_rtc_wr_toggle";

TIMESPEC "ts_cpu_rtc_wr_toggle" = FROM "cpu_rtc_wr_toggle" TO "resync_cpu_rtc_wr_toggle" TIG;

INST "*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/new_be*"

TNM = FFS "rtc_cpu_sample";

INST "*top/rtc_inst/rtc_configuration_inst/rtc_cpu_reclock/new_addr*"

TNM = FFS "rtc_cpu_sample";

TIMESPEC "ts_rtc_cpu_sample" = FROM "cpu_bus" TO "rtc_cpu_sample" 16 ns

DATAPATHONLY;

108 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |