Chapter 15: Detailed Example Design (Standard Format)

Viewing the Simulation Wave Form

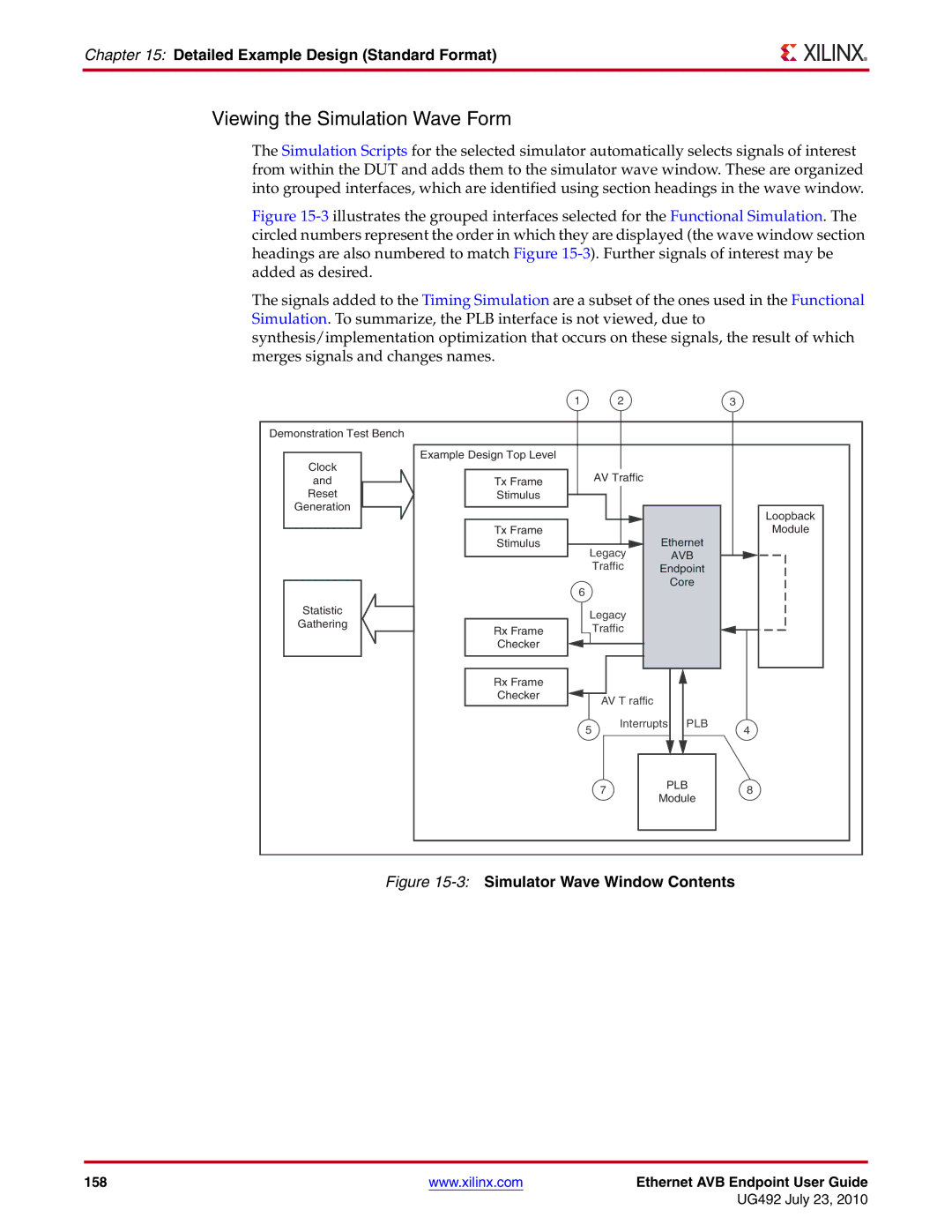

The Simulation Scripts for the selected simulator automatically selects signals of interest from within the DUT and adds them to the simulator wave window. These are organized into grouped interfaces, which are identified using section headings in the wave window.

Figure 15-3 illustrates the grouped interfaces selected for the Functional Simulation. The circled numbers represent the order in which they are displayed (the wave window section headings are also numbered to match Figure 15-3). Further signals of interest may be added as desired.

The signals added to the Timing Simulation are a subset of the ones used in the Functional Simulation. To summarize, the PLB interface is not viewed, due to synthesis/implementation optimization that occurs on these signals, the result of which merges signals and changes names.

Demonstration Test Bench

Clock

and

Reset

Generation

Statistic

Gathering

1 |

| 2 |

|

| 3 |

Example Design Top Level |

|

|

|

|

|

Tx Frame |

| AV Traffic |

|

|

|

|

|

|

|

| |

Stimulus |

|

|

|

|

|

|

|

|

|

| Loopback |

Tx Frame |

|

| Ethernet | Module | |

Stimulus | Legacy |

| |||

|

| AVB |

| ||

|

| Traffic | Endpoint |

| |

6 |

|

|

| Core |

|

|

|

|

|

| |

| Legacy |

|

|

| |

Rx Frame |

| Traffic |

|

|

|

Checker |

|

|

|

|

|

Rx Frame |

|

|

|

|

|

Checker |

| AV T raffic |

|

|

|

|

|

|

|

| |

| 5 | Interrupts | PLB | 4 | |

|

|

|

| ||

|

| 7 | PLB | 8 | |

|

| Module | |||

|

|

|

| ||

Figure 15-3: Simulator Wave Window Contents

158 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |