Chapter 7: Ethernet AVB Endpoint Reception

rx_clk

rx_clk_enable

legacy_rx_data[7:0]

![]() DA

DA ![]()

![]() SA

SA ![]() L/T

L/T ![]() DATA

DATA

legacy_rx_data_valid

legacy_rx_frame_good

legacy_rx_frame_bad

legacy_rx_filter_match[0]

legacy_rx_filter_match[1]

legacy_rx_filter_match[2]

legacy_rx_filter_match[3]

legacy_rx_filter_match[4]

legacy_rx_filter_match[5]

legacy_rx_filter_match[6]

legacy_rx_filter_match[7]

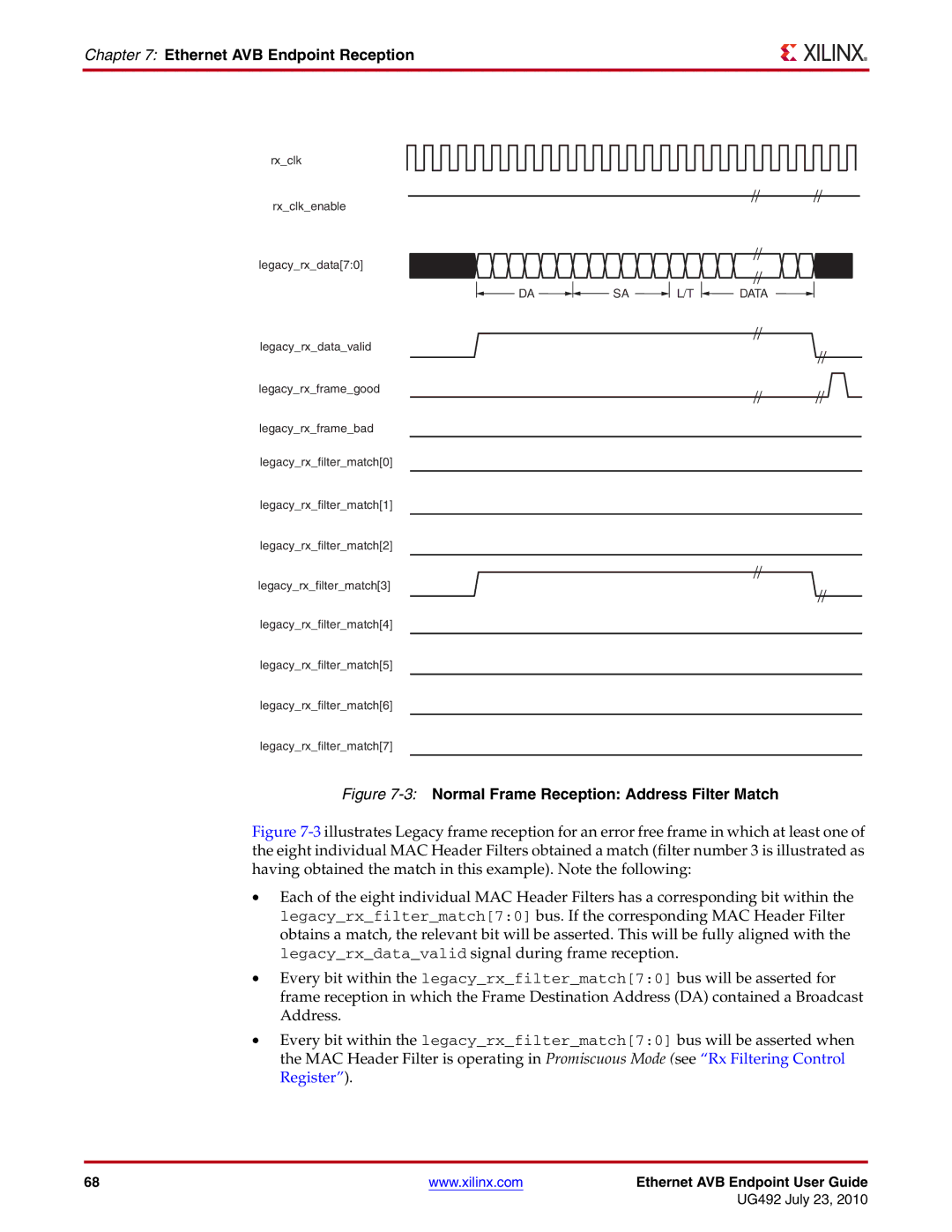

Figure 7-3: Normal Frame Reception: Address Filter Match

Figure 7-3 illustrates Legacy frame reception for an error free frame in which at least one of the eight individual MAC Header Filters obtained a match (filter number 3 is illustrated as having obtained the match in this example). Note the following:

•Each of the eight individual MAC Header Filters has a corresponding bit within the legacy_rx_filter_match[7:0] bus. If the corresponding MAC Header Filter obtains a match, the relevant bit will be asserted. This will be fully aligned with the legacy_rx_data_valid signal during frame reception.

•Every bit within the legacy_rx_filter_match[7:0] frame reception in which the Frame Destination Address Address.

bus will be asserted for (DA) contained a Broadcast

•Every bit within the legacy_rx_filter_match[7:0] bus will be asserted when the MAC Header Filter is operating in Promiscuous Mode (see “Rx Filtering Control Register”).

68 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |