Chapter 15: Detailed Example Design (Standard Format)

Timing Simulation

The test script is a ModelSim, IES, or VCS macro that automates the simulation of the test bench and is in the following location:

<project_dir>/<component_name>/simulation/timing/

The test script performs the following tasks:

•Compiles the

•Compiles the demonstration test bench

•Starts a simulation of the test bench using

•Opens a Wave window and adds signals of interest

•Runs the simulation to completion

Example Design

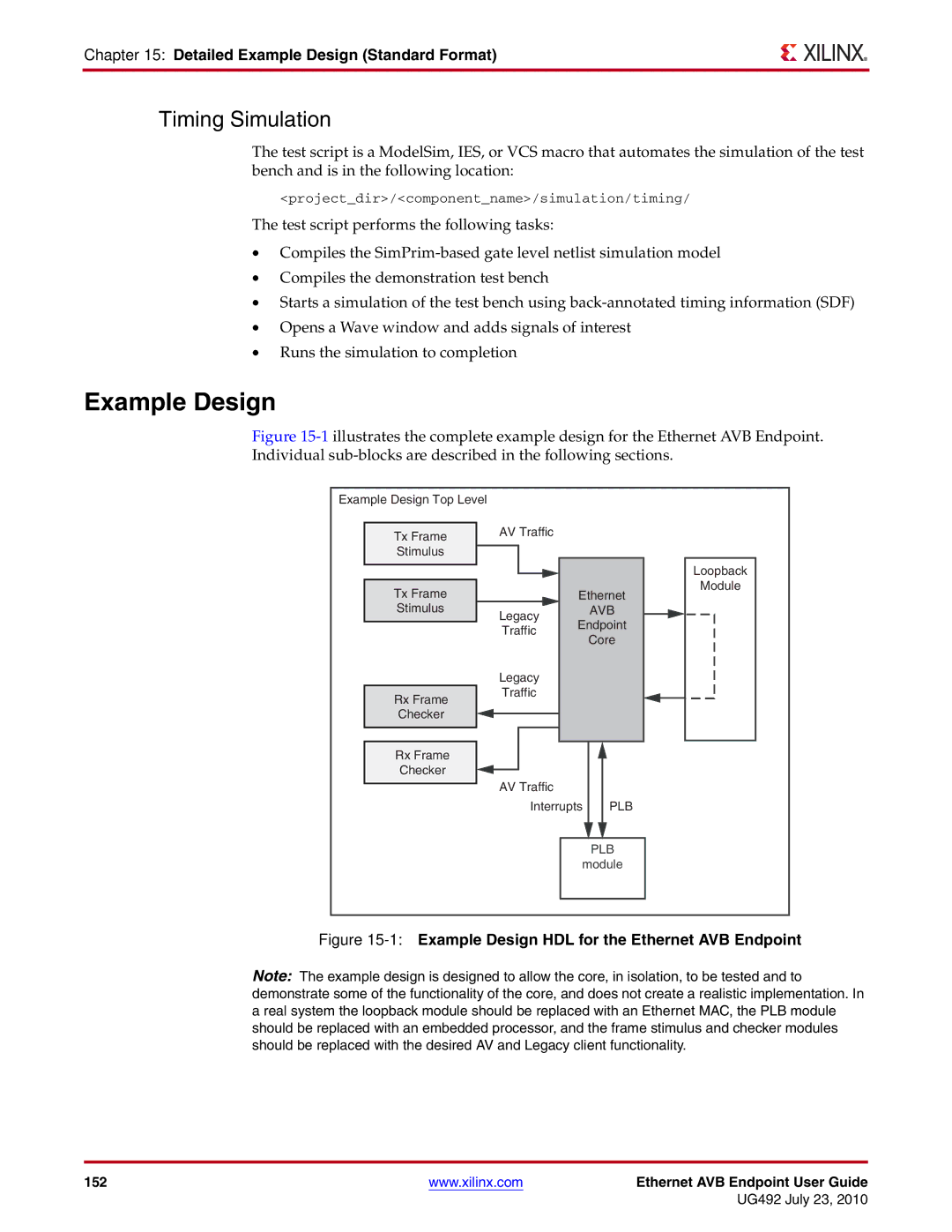

Figure 15-1 illustrates the complete example design for the Ethernet AVB Endpoint.

Individual sub-blocks are described in the following sections.

Example Design Top Level |

|

|

|

Tx Frame | AV Traffic |

|

|

|

|

| |

Stimulus |

|

|

|

|

|

| Loopback |

Tx Frame |

|

| Module |

| Ethernet | ||

Stimulus | Legacy |

| AVB |

| Endpoint | ||

| Traffic | ||

|

| Core | |

|

|

| |

| Legacy |

|

|

Rx Frame | Traffic |

|

|

|

|

| |

Checker |

|

|

|

Rx Frame |

|

|

|

Checker |

|

|

|

| AV Traffic |

|

|

| Interrupts | PLB | |

|

|

| PLB |

|

| module | |

Figure | |||

Note: The example design is designed to allow the core, in isolation, to be tested and to demonstrate some of the functionality of the core, and does not create a realistic implementation. In a real system the loopback module should be replaced with an Ethernet MAC, the PLB module should be replaced with an embedded processor, and the frame stimulus and checker modules should be replaced with the desired AV and Legacy client functionality.

152 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

UG492 July 23, 2010