Chapter 6: Ethernet AVB Endpoint Transmission

Error Free Legacy Frame Transmission

tx_clk

tx_clk_enable

legacy_tx_data[7:0]

legacy_tx_data_valid

legacy_tx_ack

legacy_tx_underrun

DA | SA | L/T | DATA |

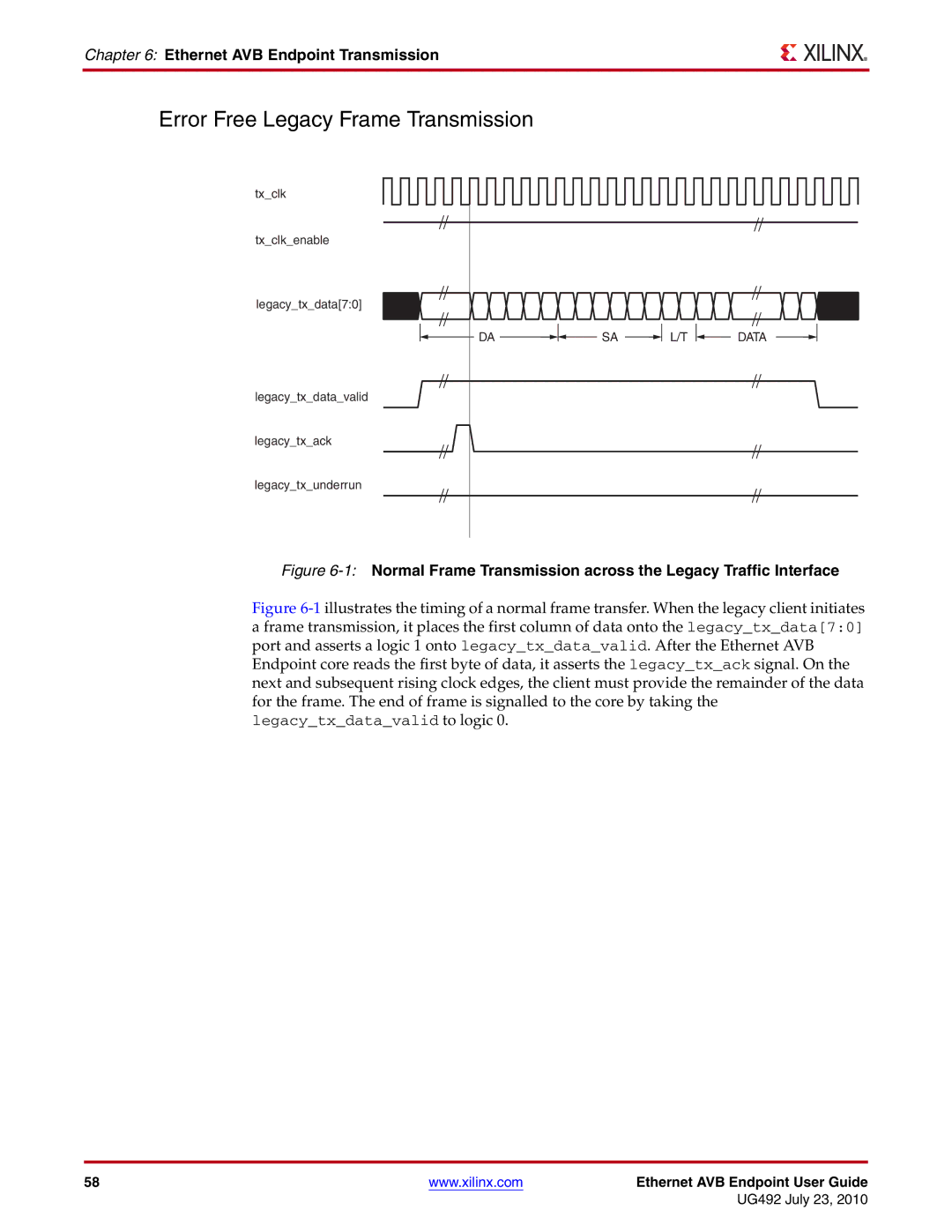

Figure 6-1: Normal Frame Transmission across the Legacy Traffic Interface

Figure 6-1 illustrates the timing of a normal frame transfer. When the legacy client initiates

aframe transmission, it places the first column of data onto the legacy_tx_data[7:0] port and asserts a logic 1 onto legacy_tx_data_valid. After the Ethernet AVB Endpoint core reads the first byte of data, it asserts the legacy_tx_ack signal. On the next and subsequent rising clock edges, the client must provide the remainder of the data for the frame. The end of frame is signalled to the core by taking the legacy_tx_data_valid to logic 0.

58 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |