Chapter 15: Detailed Example Design (Standard Format)

Table

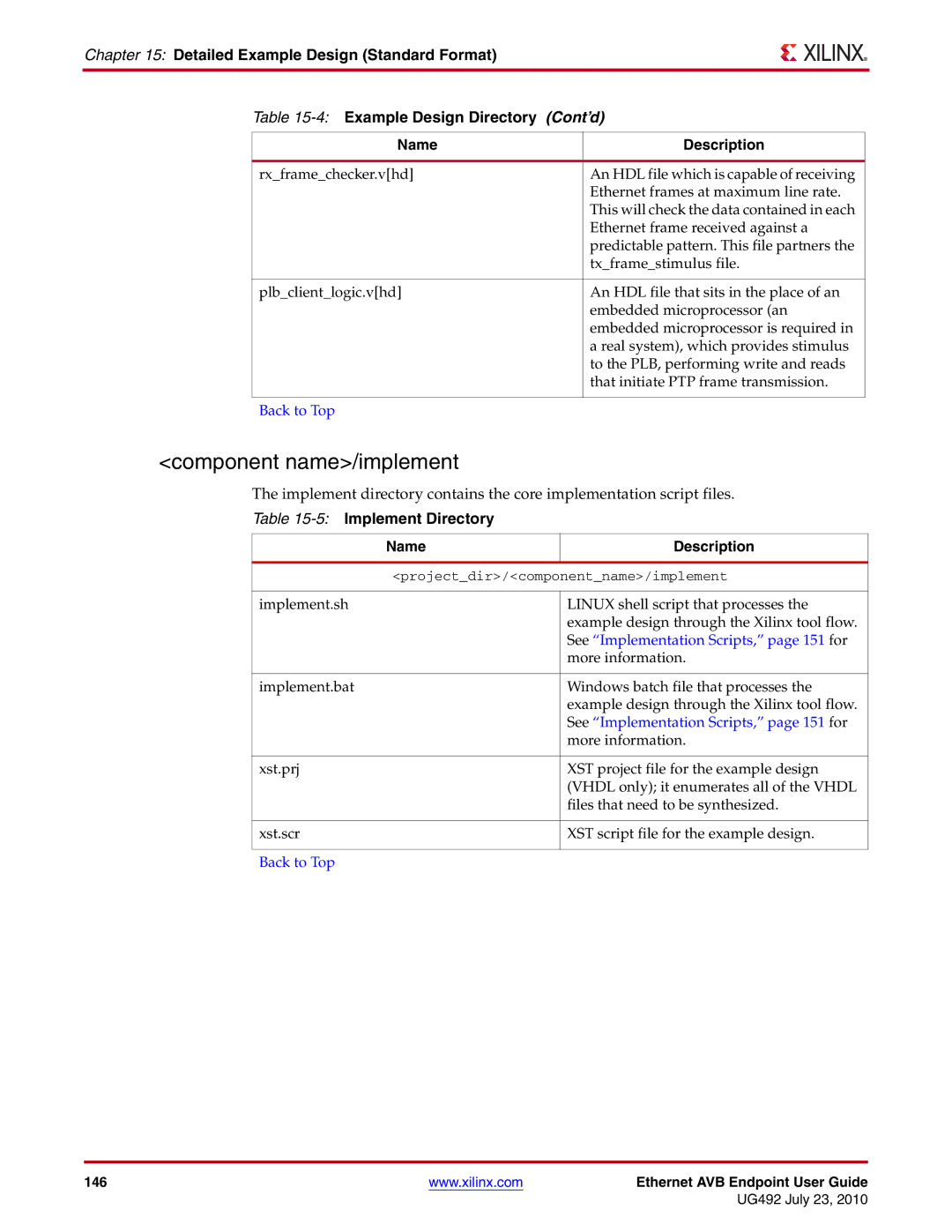

Name | Description |

|

|

rx_frame_checker.v[hd] | An HDL file which is capable of receiving |

| Ethernet frames at maximum line rate. |

| This will check the data contained in each |

| Ethernet frame received against a |

| predictable pattern. This file partners the |

| tx_frame_stimulus file. |

|

|

plb_client_logic.v[hd] | An HDL file that sits in the place of an |

| embedded microprocessor (an |

| embedded microprocessor is required in |

| a real system), which provides stimulus |

| to the PLB, performing write and reads |

| that initiate PTP frame transmission. |

|

|

Back to Top |

|

<component name>/implement

The implement directory contains the core implementation script files.

Table 15-5: Implement Directory

Name | Description |

|

|

<project_dir>/<component_name>/implement

implement.sh

implement.bat

xst.prj

xst.scr

Back to Top

LINUX shell script that processes the example design through the Xilinx tool flow. See “Implementation Scripts,” page 151 for more information.

Windows batch file that processes the example design through the Xilinx tool flow. See “Implementation Scripts,” page 151 for more information.

XST project file for the example design (VHDL only); it enumerates all of the VHDL files that need to be synthesized.

XST script file for the example design.

146 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |