Directory and File Contents

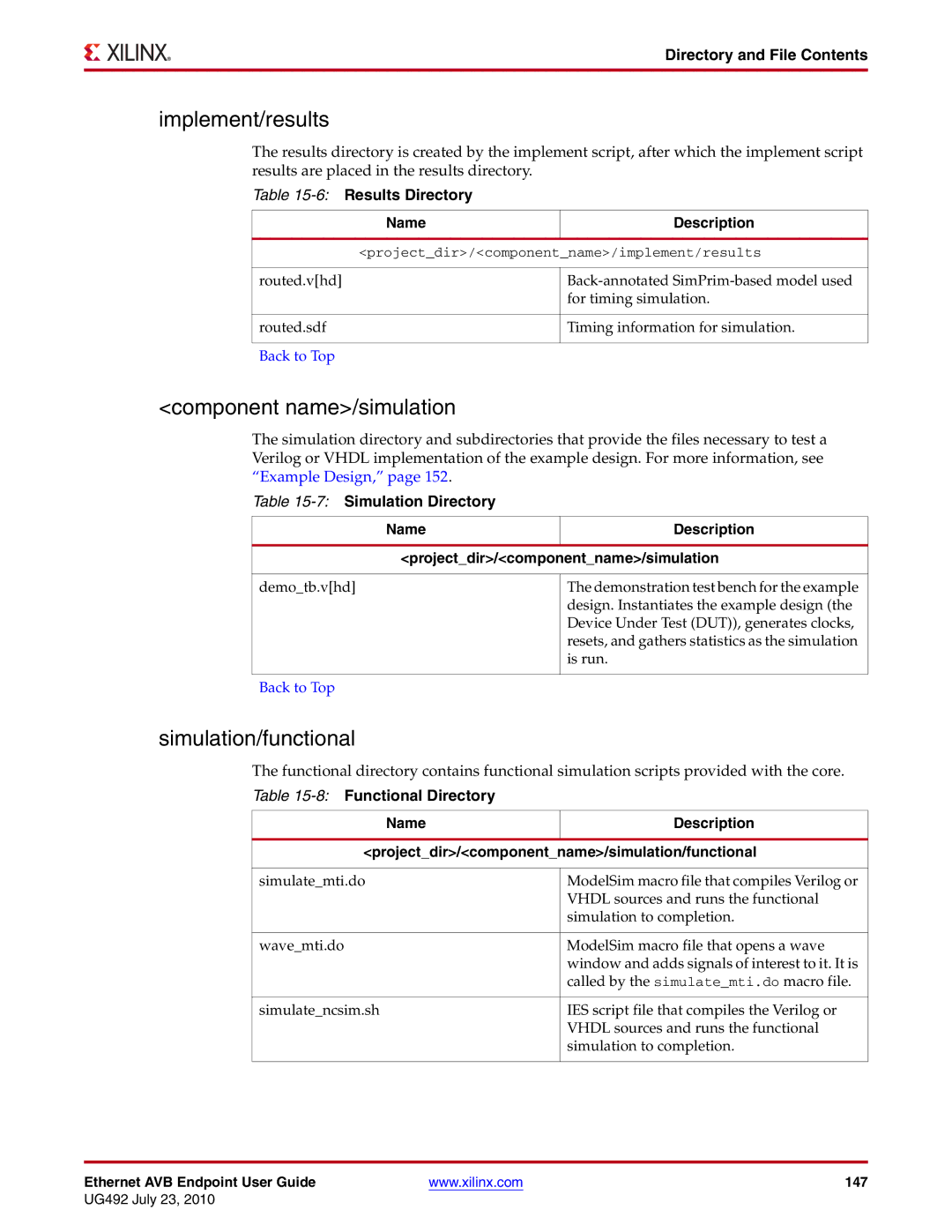

implement/results

The results directory is created by the implement script, after which the implement script results are placed in the results directory.

Table 15-6: Results Directory

Name | Description |

|

|

<project_dir>/<component_name>/implement/results

routed.v[hd]

routed.sdf

Back to Top

Timing information for simulation.

<component name>/simulation

The simulation directory and subdirectories that provide the files necessary to test a Verilog or VHDL implementation of the example design. For more information, see “Example Design,” page 152.

Table

Name | Description |

|

|

<project_dir>/<component_name>/simulation

demo_tb.v[hd]

Back to Top

The demonstration test bench for the example design. Instantiates the example design (the Device Under Test (DUT)), generates clocks, resets, and gathers statistics as the simulation is run.

simulation/functional

The functional directory contains functional simulation scripts provided with the core.

Table

Name | Description |

|

|

<project_dir>/<component_name>/simulation/functional | |

|

|

simulate_mti.do | ModelSim macro file that compiles Verilog or |

| VHDL sources and runs the functional |

| simulation to completion. |

|

|

wave_mti.do | ModelSim macro file that opens a wave |

| window and adds signals of interest to it. It is |

| called by the simulate_mti.do macro file. |

|

|

simulate_ncsim.sh | IES script file that compiles the Verilog or |

| VHDL sources and runs the functional |

| simulation to completion. |

|

|

Ethernet AVB Endpoint User Guide | www.xilinx.com | 147 |

UG492 July 23, 2010