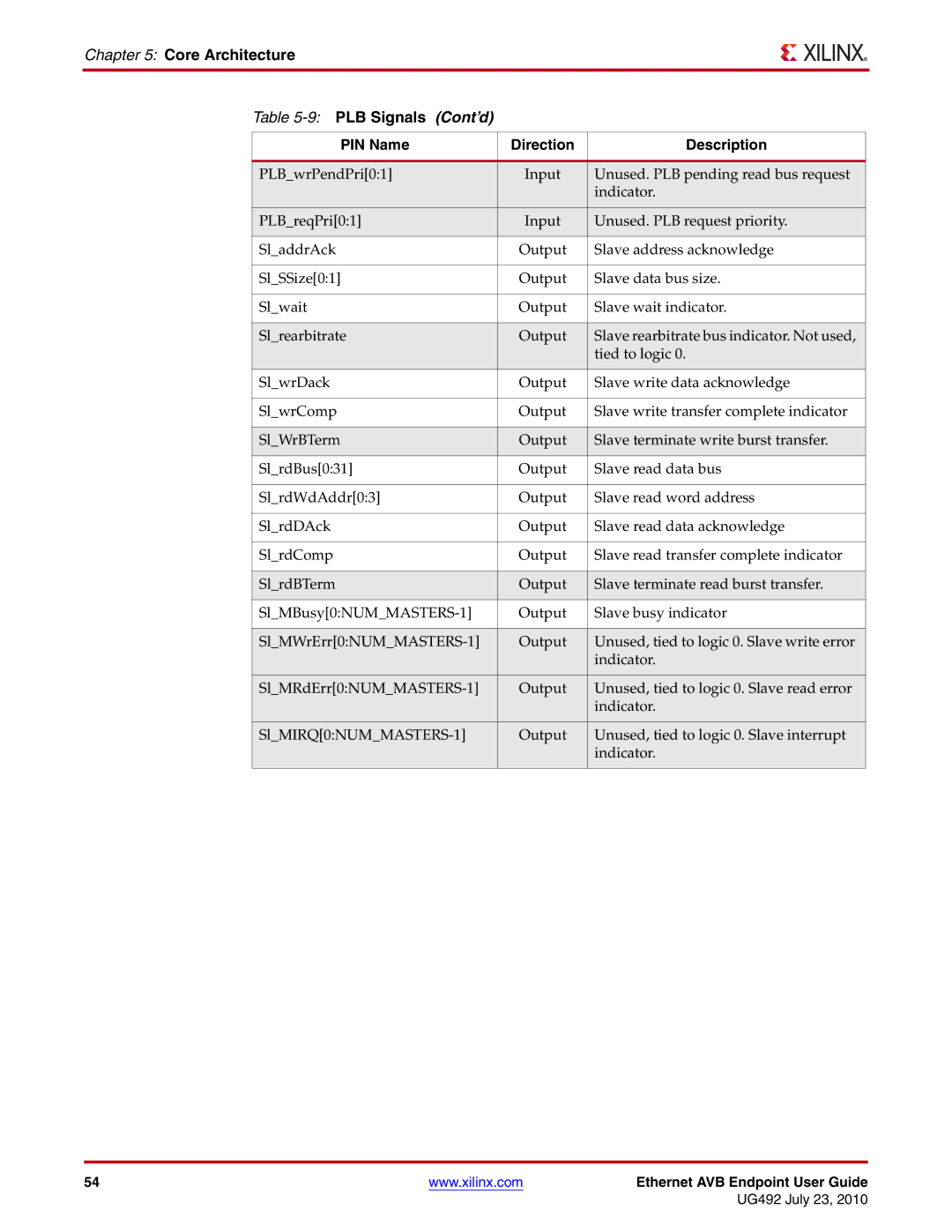

Chapter 5: Core Architecture

Table

PIN Name | Direction | Description |

|

|

|

PLB_wrPendPri[0:1] | Input | Unused. PLB pending read bus request |

|

| indicator. |

|

|

|

PLB_reqPri[0:1] | Input | Unused. PLB request priority. |

|

|

|

Sl_addrAck | Output | Slave address acknowledge |

|

|

|

Sl_SSize[0:1] | Output | Slave data bus size. |

|

|

|

Sl_wait | Output | Slave wait indicator. |

|

|

|

Sl_rearbitrate | Output | Slave rearbitrate bus indicator. Not used, |

|

| tied to logic 0. |

|

|

|

Sl_wrDack | Output | Slave write data acknowledge |

|

|

|

Sl_wrComp | Output | Slave write transfer complete indicator |

|

|

|

Sl_WrBTerm | Output | Slave terminate write burst transfer. |

|

|

|

Sl_rdBus[0:31] | Output | Slave read data bus |

|

|

|

Sl_rdWdAddr[0:3] | Output | Slave read word address |

|

|

|

Sl_rdDAck | Output | Slave read data acknowledge |

|

|

|

Sl_rdComp | Output | Slave read transfer complete indicator |

|

|

|

Sl_rdBTerm | Output | Slave terminate read burst transfer. |

|

|

|

Output | Slave busy indicator | |

|

|

|

Output | Unused, tied to logic 0. Slave write error | |

|

| indicator. |

|

|

|

Output | Unused, tied to logic 0. Slave read error | |

|

| indicator. |

|

|

|

Output | Unused, tied to logic 0. Slave interrupt | |

|

| indicator. |

|

|

|

54 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |