Chapter 14: Quick Start Example Design

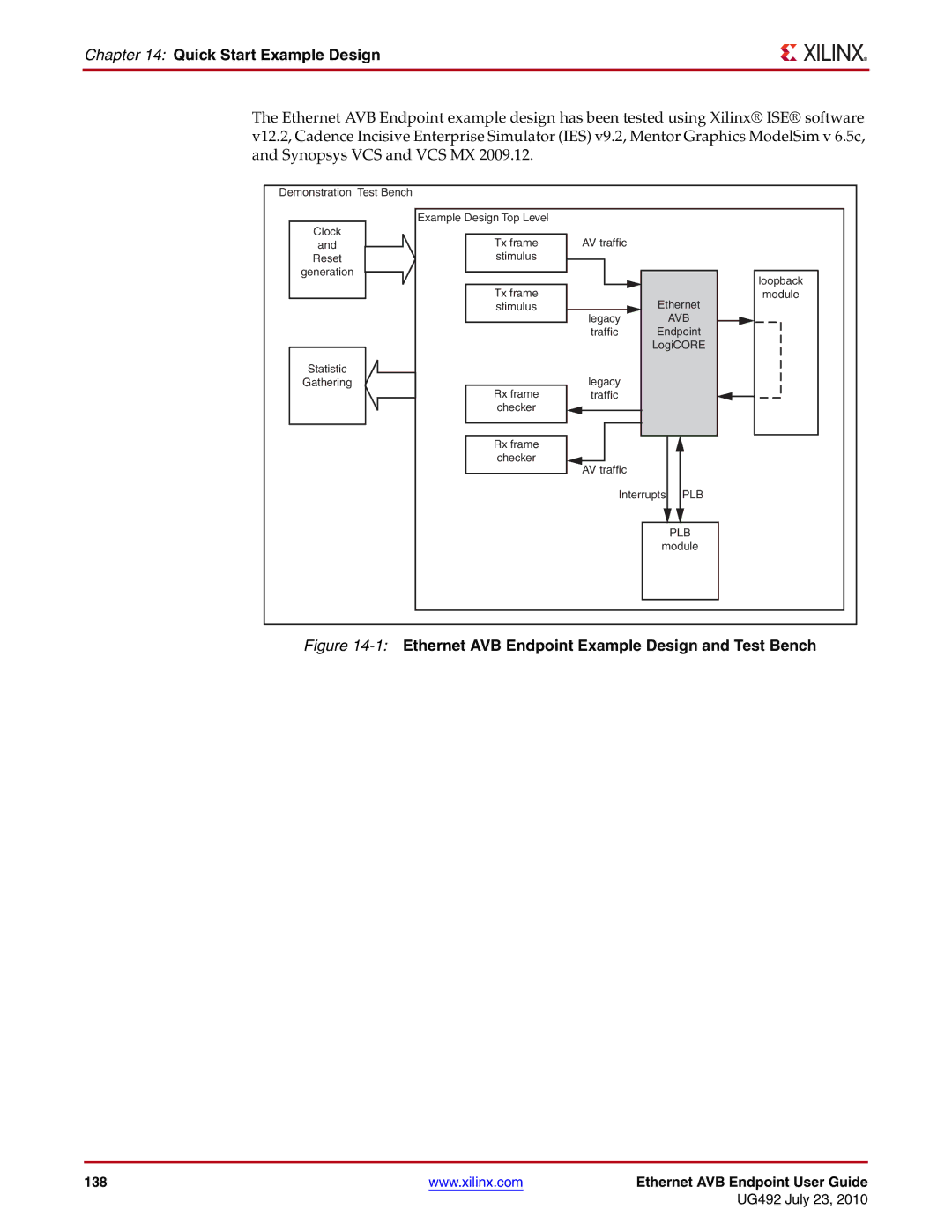

The Ethernet AVB Endpoint example design has been tested using Xilinx® ISE® software v12.2, Cadence Incisive Enterprise Simulator (IES) v9.2, Mentor Graphics ModelSim v 6.5c, and Synopsys VCS and VCS MX 2009.12.

Demonstration Test Bench

Clock

and

Reset

generation

Statistic

Gathering

Example Design Top Level |

|

|

|

Tx frame | AV traffic |

|

|

stimulus |

|

|

|

Tx frame |

|

| loopback |

|

| module | |

stimulus |

| Ethernet | |

| legacy |

| AVB |

| traffic | Endpoint | |

|

| LogiCORE | |

Rx frame | legacy |

|

|

traffic |

|

| |

checker |

|

|

|

Rx frame |

|

|

|

checker | AV traffic |

|

|

|

|

| |

| Interrupts | PLB | |

|

|

| PLB |

|

| module | |

Figure 14-1: Ethernet AVB Endpoint Example Design and Test Bench

138 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |