Chapter 9: Precise Timing Protocol Packet Buffers

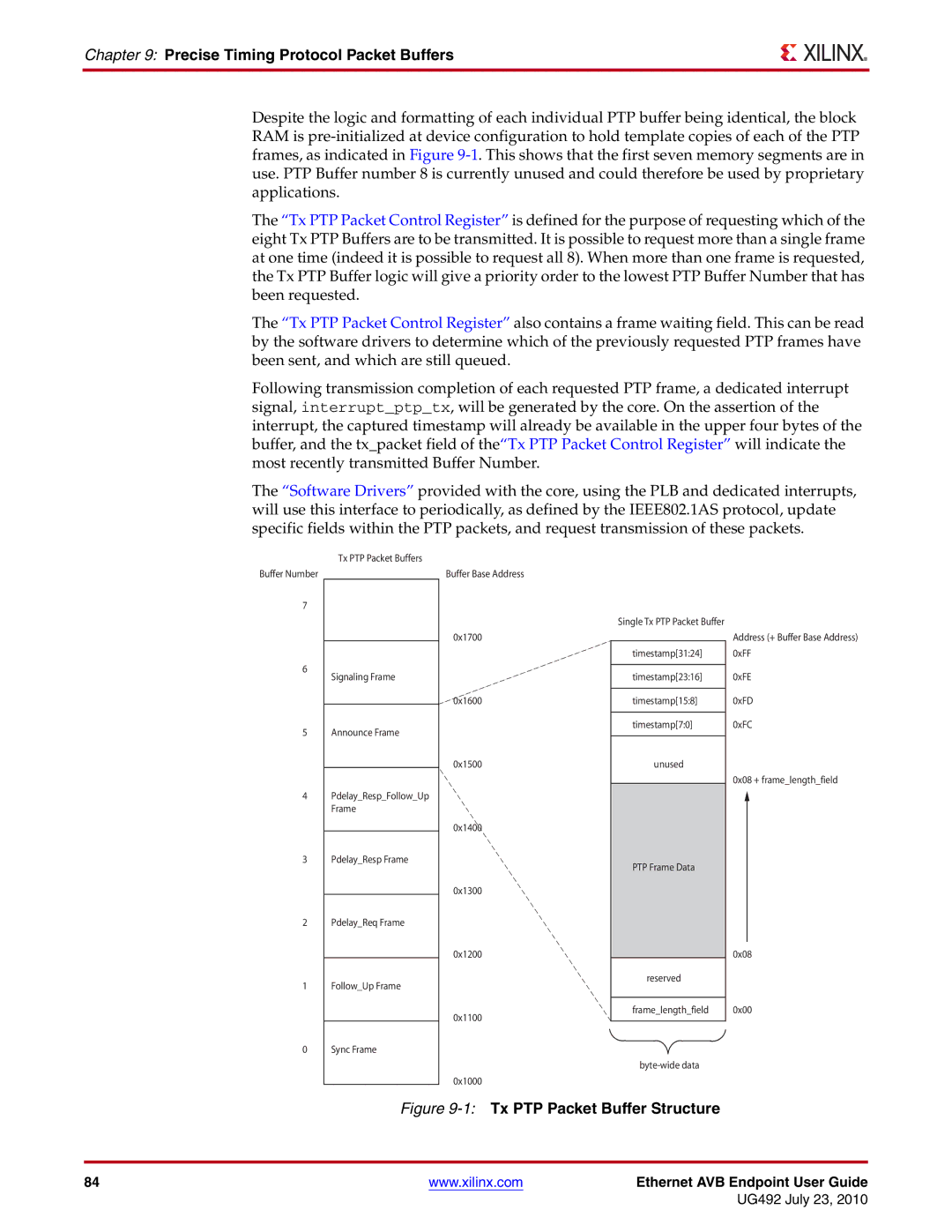

Despite the logic and formatting of each individual PTP buffer being identical, the block RAM is

The “Tx PTP Packet Control Register” is defined for the purpose of requesting which of the eight Tx PTP Buffers are to be transmitted. It is possible to request more than a single frame at one time (indeed it is possible to request all 8). When more than one frame is requested, the Tx PTP Buffer logic will give a priority order to the lowest PTP Buffer Number that has been requested.

The “Tx PTP Packet Control Register” also contains a frame waiting field. This can be read by the software drivers to determine which of the previously requested PTP frames have been sent, and which are still queued.

Following transmission completion of each requested PTP frame, a dedicated interrupt signal, interrupt_ptp_tx, will be generated by the core. On the assertion of the interrupt, the captured timestamp will already be available in the upper four bytes of the buffer, and the tx_packet field of the“Tx PTP Packet Control Register” will indicate the most recently transmitted Buffer Number.

The “Software Drivers” provided with the core, using the PLB and dedicated interrupts, will use this interface to periodically, as defined by the IEEE802.1AS protocol, update specific fields within the PTP packets, and request transmission of these packets.

Buffer Number

7

6

5

4

3

2

1

0

Tx PTP Packet Buffers

Signaling Frame

Announce Frame

Pdelay_Resp_Follow_Up Frame

Pdelay_Resp Frame

Pdelay_Req Frame

Follow_Up Frame

Sync Frame

Buffer Base Address |

|

|

| |

| Single Tx PTP Packet Buffer |

|

| |

0x1700 |

| Address (+ Buffer Base Address) | ||

| timestamp[31:24] | 0xFF | ||

| timestamp[23:16] | 0xFE | ||

0x1600 | timestamp[15:8] | 0xFD | ||

| timestamp[7:0] | 0xFC | ||

0x1500 | unused |

|

| |

0x1400 |

| 0x08 + frame_length_field | ||

|

|

| ||

|

|

| ||

| PTP Frame Data |

|

| |

0x1300 |

|

|

| |

|

|

|

| |

0x1200 |

| 0x08 | ||

reserved | ||||

|

|

| ||

0x1100 | frame_length_field | 0x00 | ||

|

|

| ||

0x1000

Figure 9-1: Tx PTP Packet Buffer Structure

84 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |