Required Constraints

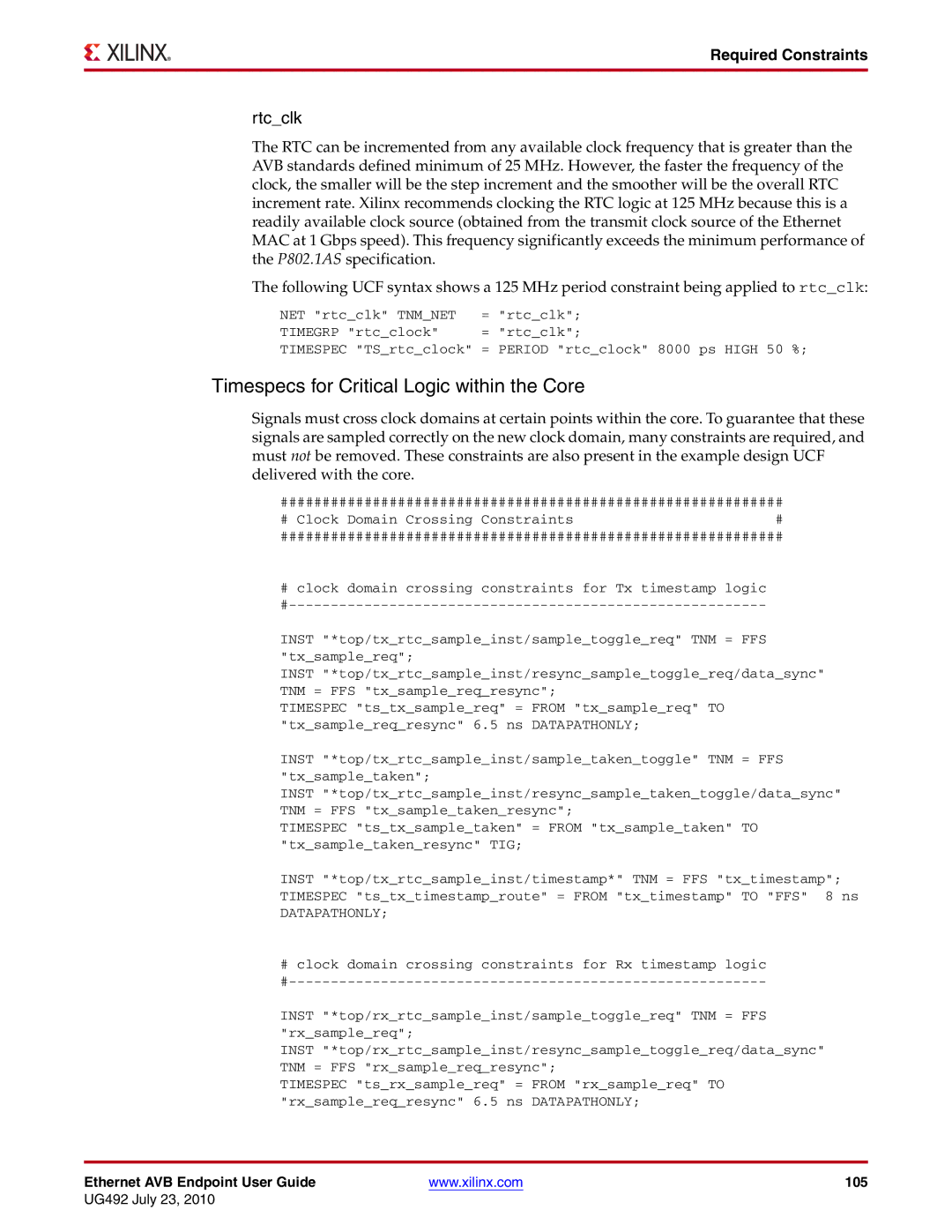

rtc_clk

The RTC can be incremented from any available clock frequency that is greater than the AVB standards defined minimum of 25 MHz. However, the faster the frequency of the clock, the smaller will be the step increment and the smoother will be the overall RTC increment rate. Xilinx recommends clocking the RTC logic at 125 MHz because this is a readily available clock source (obtained from the transmit clock source of the Ethernet MAC at 1 Gbps speed). This frequency significantly exceeds the minimum performance of the P802.1AS specification.

The following UCF syntax shows a 125 MHz period constraint being applied to rtc_clk:

NET "rtc_clk" TNM_NET | = "rtc_clk"; | |

TIMEGRP "rtc_clock" | = | "rtc_clk"; |

TIMESPEC "TS_rtc_clock" | = | PERIOD "rtc_clock" 8000 ps HIGH 50 %; |

Timespecs for Critical Logic within the Core

Signals must cross clock domains at certain points within the core. To guarantee that these signals are sampled correctly on the new clock domain, many constraints are required, and must not be removed. These constraints are also present in the example design UCF delivered with the core.

############################################################

# Clock Domain Crossing Constraints#

############################################################

#clock domain crossing constraints for Tx timestamp logic

INST "*top/tx_rtc_sample_inst/sample_toggle_req" TNM = FFS "tx_sample_req";

INST "*top/tx_rtc_sample_inst/resync_sample_toggle_req/data_sync" TNM = FFS "tx_sample_req_resync";

TIMESPEC "ts_tx_sample_req" = FROM "tx_sample_req" TO "tx_sample_req_resync" 6.5 ns DATAPATHONLY;

INST "*top/tx_rtc_sample_inst/sample_taken_toggle" TNM = FFS "tx_sample_taken";

INST "*top/tx_rtc_sample_inst/resync_sample_taken_toggle/data_sync" TNM = FFS "tx_sample_taken_resync";

TIMESPEC "ts_tx_sample_taken" = FROM "tx_sample_taken" TO "tx_sample_taken_resync" TIG;

INST "*top/tx_rtc_sample_inst/timestamp*" TNM = FFS "tx_timestamp";

TIMESPEC "ts_tx_timestamp_route" = FROM "tx_timestamp" TO "FFS" 8 ns

DATAPATHONLY;

#clock domain crossing constraints for Rx timestamp logic

INST "*top/rx_rtc_sample_inst/sample_toggle_req" TNM = FFS "rx_sample_req";

INST "*top/rx_rtc_sample_inst/resync_sample_toggle_req/data_sync" TNM = FFS "rx_sample_req_resync";

TIMESPEC "ts_rx_sample_req" = FROM "rx_sample_req" TO "rx_sample_req_resync" 6.5 ns DATAPATHONLY;

Ethernet AVB Endpoint User Guide | www.xilinx.com | 105 |

UG492 July 23, 2010