Chapter 13: Software Drivers

Core Initialization

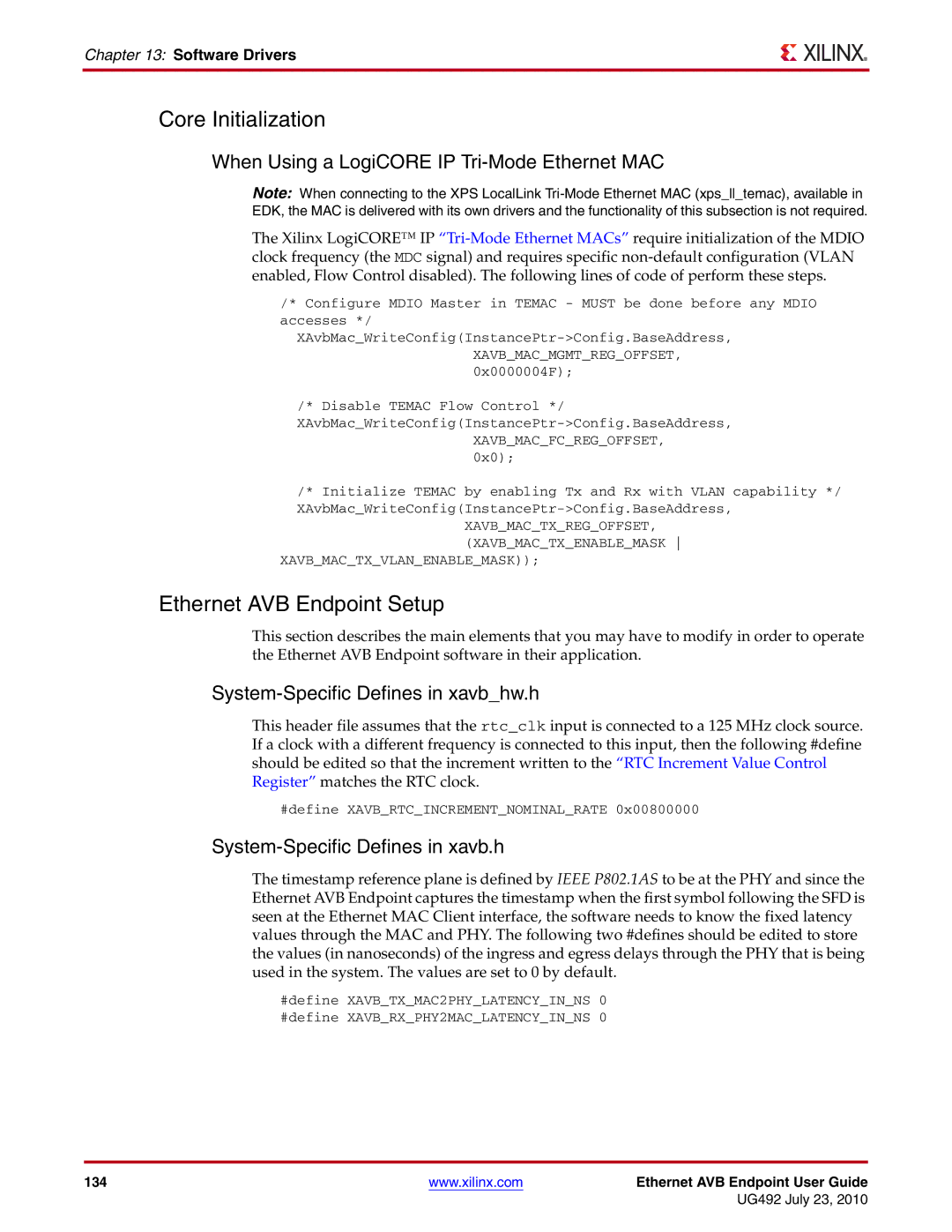

When Using a LogiCORE IP Tri-Mode Ethernet MAC

Note: When connecting to the XPS LocalLink

The Xilinx LogiCORE™ IP

/* Configure MDIO Master in TEMAC - MUST be done before any MDIO accesses */

/* Disable TEMAC Flow Control */

0x0);

/* Initialize TEMAC by enabling Tx and Rx with VLAN capability */

XAVB_MAC_TX_REG_OFFSET, (XAVB_MAC_TX_ENABLE_MASK

XAVB_MAC_TX_VLAN_ENABLE_MASK));

Ethernet AVB Endpoint Setup

This section describes the main elements that you may have to modify in order to operate the Ethernet AVB Endpoint software in their application.

System-Specific Defines in xavb_hw.h

This header file assumes that the rtc_clk input is connected to a 125 MHz clock source. If a clock with a different frequency is connected to this input, then the following #define should be edited so that the increment written to the “RTC Increment Value Control Register” matches the RTC clock.

#define XAVB_RTC_INCREMENT_NOMINAL_RATE 0x00800000

System-Specific Defines in xavb.h

The timestamp reference plane is defined by IEEE P802.1AS to be at the PHY and since the Ethernet AVB Endpoint captures the timestamp when the first symbol following the SFD is seen at the Ethernet MAC Client interface, the software needs to know the fixed latency values through the MAC and PHY. The following two #defines should be edited to store the values (in nanoseconds) of the ingress and egress delays through the PHY that is being used in the system. The values are set to 0 by default.

#define XAVB_TX_MAC2PHY_LATENCY_IN_NS 0 #define XAVB_RX_PHY2MAC_LATENCY_IN_NS 0

134 | www.xilinx.com | Ethernet AVB Endpoint User Guide |

|

| UG492 July 23, 2010 |